基于Microblaze软核的嵌入式系统设计

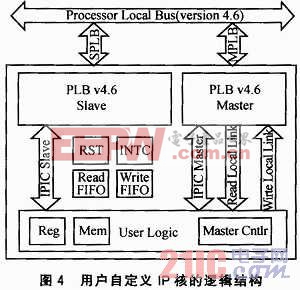

②定制用户自己的IP核。由于嵌入式系统开发的特殊性,有时可能很难找到一款ASIC控制器,具备系统要求的所有外设接口。在这种情况下,要么用软件实现所缺的外设功能,从而牺牲了系统性能;要么单独购置一片该接口芯片,从而增大了电路板面积和成本。而基于FPGA软核的设计则不存在这种问题。在XPS中定制用户IP核与一般用VHDL编写逻辑电路不同的是,这种定制IP可以挂接在PLB总线上,从而实现与Microblaze的通信。XPS提供自定义IP核的生成向导,图4给出了用户自定义IP核的逻辑结构。从图可以看出,生成向导创建了两个模块,一个是与PLB总线进行交互的接口模块IPIF,另一个是用户逻辑模块User_Logic。IPIF完成PLB总线信号的捕捉和协议转换,这部分内容不需要用户参与,用户只需根据自定义逻辑的输入/输出信号在IPIF中给出相应的声明即可;User_Logic模块则是需要用户进行手动添加自定义逻辑代码的地方,在这里用户只需关注自己需要实现的功能,不用担心它们与Microblaze之间的通信链接。本文引用地址:https://www.eepw.com.cn/article/150858.htm

2.2 软件平台的开发

EDK的另一个组件SDK是对于XPS集成开发环境的补充,提供了一个软件工程项目的开发环境,具有以下功能和特点:

◆基于Eclipse开源代码标准;

◆项目管理;

◆功能完善的C/C++代码编辑和编译环境;

◆程序创建配置和自动化的Makefile生成;

◆完美集成的对嵌入式对象的无缝调试环境。

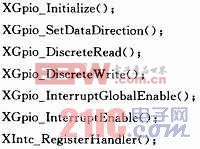

除了提供软件的开发环境外,Xilinx公司还提供了各种IP核的API控制函数,这些API被安放在..\EDK\SW\XilinxProcessorIPLib\drivers目录下,其中..\表示Xilinx软件的安装目录。通过阅读IP核的PDF说明文档和API函数的C代码,用户可以很容易地实现对IP核的控制。以通用输入/输出端口GPIO为例,在文件夹..\EDK\sw\XilinxProcessorIPLib\drivers\gpio_v2_13_a下存放着与GPIO软件编程有关的所有内容,其src子目录下包含各种API函数的C源码,doc目录下包含对各种API函数的使用说明,而examples目录下还有针对GPIO进行编程的实例源码。一般对GPIO的操作过程为:

即首先对GPIO口进行初始化,然后设置其方向为输入或是输出,接下来就可以对GPIO进行读写。如果该GPIO可以产生中断,则必须置位其中断使能位,然后将中断处理函数挂接到中断控制器或直接挂到Microblaze的中断位上。

评论