基于DSP的FPGA配置方法研究与实现

2 硬件实现电路

2.1 硬件结构

本文选用AD公司生产的ADSP-TS101这款芯片作为配置FPGA的主处理器。ADSP-TS101是一款极高性能的静态超标量处理器,同时支持浮点和定点处理,最高工作频率为300 MHz,地址范围4 GB,最大支持16MB的PROM。从地址的0x08000000~0xFFFFFFFF为外部存储器空间的一部分,可以访问独立的外围设备,完全可以满足片外程序的寻址。为了完成配置FPGA的时序,需要DSP有灵活可控的引脚信号。而ADSP-TS101的4个标志引脚信号FLAG3~FLAG0允许在ADSP-TS101和其他的设备之间传递位信号。任何一个标志引脚既可以作为输入也可以作为输出,且ADSP -TS101的许多指令都可以以标志引脚的输入作为执行条件,可以在多处理器和其他接口之间进行高效的通信和同步。因此,可以将此4个管脚和FPGA进行连接,模拟完成FPGA的配置时序。

存储芯片选用Spansion公司的高性能FLASH芯片S29JL064H,最小访问周期为55 ns,其可以配置成8M×8 b的存储方式。而Virtex-Ⅱ系列FPGA的配置数据包括配置数据帧和配置寄存器数据,配置寄存器数据都为40×32 b,即1 280 b,配置数据帧会因器件不同而有变化,对于XC2V1000器件来说,配置数据帧为4 082 592 b,总的配置数据不到4 Mb。所以,此存储芯片完全可以满足FPGA和DSP程序的存储。对于FLASH存储空间的划分,采用一分为二的方法,DSP和FPGA程序各占一半空间。即,从地址0x00000~0x3FFFFF这4 MB空间用来存储DSP程序,剩余的

4MB空间0x400000~0x7FFFFF存储FPGA程序。本文引用地址:https://www.eepw.com.cn/article/149314.htm

系统的硬件结构示意图如图1所示。由DSP的RD信号充当FPGA的配置时钟CCLK,FLAG0信号模拟FPGA的PROG_B信号,FLAG1和FLAG2分别作为FPGA的DONE信号和BUSY信号的输入。此系统在设计时,采用了DSP,FPGA,FLASH共用数据总线的方式,所以当DSP从FLASH芯片中读取FPGA的加载数据并出现在总线上的时候,可以直接被FPGA抓取来完成FPGA程序的正常加载。

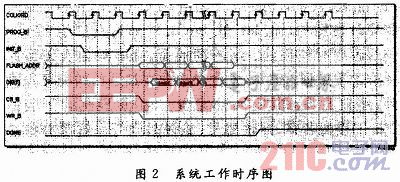

2.2 工作时序

系统上电后,DSP启动DMA通道0,从FLASH地址0开始,把一个256 word的程序块传送到内部存储器地址0x00~0xFF。然后,DSP开始从0x00执行加载核,加载核将后续应用代码和数据加载至地址0xFF之后的内部存储器内。最后,加载核启动一个256 word的DMA,使其自身被工作程序代码覆盖。至此,DSP即从地址0x00开始执行工作程序。在工作程序中首先从FLASH存储器中读取FPGA的加载程序,并给出相应的加载时序,完成FPGA程序加载。具体的工作时序,如图2所示。

3 结语

随着FPGA+DSP的系统结构在电子设计领域中应用的日益广泛化,在不增加其它额外器件的前提下,依靠DSP模拟FPGA加载时序,对FPGA使用了被动并行的配置方式。此方法在一定程度减少了设计冗余,实现了小型化和低成本。应用于电路系统中,工作稳定可靠,灵活高效。

评论