基于DSP开发系统设计与实现

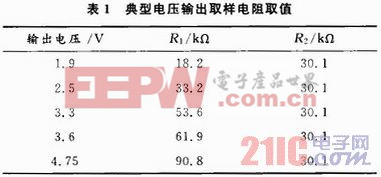

TPS767D301的输出端1OUT的电压由式(1)确定:

Vo=Vref(1+R1/R2) (1)

式中:Vref=1.183 4 V为电压调整器的内部参考电压;R1和R2的取值应保证驱动电流近似为50μA。如果电阻过小,会使电流过大,消耗电力;如果电阻过大,FB引脚会出现电流脉冲尖峰,会使输出电压波动。典型电压输出时,R1和R2的取值如表1所示。本文引用地址:https://www.eepw.com.cn/article/149182.htm

为了提高输出电压的稳定性,模拟电源与数字电源之间通过铁氧体磁珠和电容进行滤波,铁氧体磁珠具有可以忽略的寄生电容,电气特性和一般的电感相似,这样可以减少来自模拟电源或其他并联电路所产生的噪声生干扰。

2 系统RAM扩展

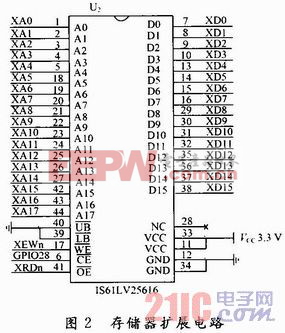

在TMS320F28335的片上已经集成了34 K×16 b的RAM,且内部RAM的访问速度可达150 MIPS,通常用于放置系统对运算速度要求较高的程序。F28335的片上还集成了256 K×16 b的FLASH,但由于FLASH烧写次数有限,而且烧写速度慢,操作麻烦。使用外扩RAM后,仿真时程序可以放入外扩RAM中运行,程序长度不受限制,这样程序的设计和调试就非常方便。在调试完成后通过修改.cmd文件等方法将程序烧进FLASH中运行。同时,外扩RAM还可以开放给其他任务。外扩RAM选用ISSI公司的IS61LV25616,存储容量为256 K×16 b,3.3 V的供电电压。使用区间6作为外扩存储区间,存储地址范围为0x100000~0x13FFFF。由于IS61LV25616的访问速度有8 ns,10 ns,12 ns,15 ns可选择,而当CPU运行在150 MHz时,地址和数据的最小有效时间为3个时钟周期,即20 ns,所以不用考虑时序问题。存储器的地址线和数据线分别对应DSP的地址线和数据线,片选端CS和DSP的GPIO28连接,存储器的读/写端口分和DSP的读/写端口连接,具体电路图如2所示。

评论