摘要:空间矢量脉宽调制算法是电压型逆变器控制方面的研究热点,广泛应用于三相电力系统中。基于硬件的FPGA/CPLD芯片能满足该算法对处理速度、实时性、可靠性较高的要求,本文利用Verilog HDL实现空间矢量脉宽调制算

关键字:

同步电动机 电压型逆变器 Verilog HDL

为了得到比传统片上网络的网络资源接口(NI)更高的数据传输效率和更加稳定的数据传输效果,提出了一种新的高效网络接口的设计方法,并采用Verilog HDL语言对相关模块进行编程,实现了高效传输功能,同时又满足核内路由的设计要求。最终通过仿真软件Xilinx ISE Design Suite 12.3和ModelSim SE 6.2b得到了满足设计要求的仿真结果。

关键字:

片上网络 网络资源接口 核内路由 Verilog HDL

基于Xilinx V5的DDR2数据解析功能实现,摘要:介绍了一种基于Xilinx V5芯片的硬件板卡上,利用Verilog硬件编程语言,来实现DDR2对数据文件解析的目的:分析了CPCI总线与FPGA之间的通信特点;然后根据收到的数据文件要求,介绍了DDR2的使用方法;最后介绍了对

关键字:

Xilinx Verilog DDR2 数据解析 信号波形

混合同余法产生随机噪声的FPGA实现,摘要:随着电子对抗技术的快速发展,在有源式干扰机中需要用到数字高斯白噪声。通过对混合同余法产生随机序列的原理研究,本文提出了一种利用FPGA产生高斯白噪声的方法。该方法在PC主控端的控制下,采用ROM查找表的方

关键字:

高斯白噪声 混合同余法 FPGA Verilog HDL

摘要:为了提高LCD1602显示效果,增强抗扰能力,文章基于TOP2812开发板,依据LCD1602操作时序要求,在开发板CPLD部分实现了LCD1602显示系统的设计。文中对

关键字:

LCD1602 显示系统 时序 Vetilog HDL

可综合的意思是说所编写的代码可以对应成具体的电路,不可综合就是所写代码没有对应的电路结构,例如行为级语法就是一种不可综合的代码,通常用于写仿真测试文件。 建立可综合模型时,需注意以下几点: 不使用initial 不使用#10之类的延时语句 不使用循环次数不确定的循环语句,如forever,while等 不使用用户自定义原语(UDP元件) 尽量使用同步方式设计电路 用always块来描述组合逻辑时,应列出所有输入信号作为敏感信号列表,即always@(*) 所有的内部寄存器都应该能够被复

关键字:

verilog FPGA

//基本D触发器 module D_EF(Q,D,CLK) input D,CLK; output Q; reg Q; //在always语句中被赋值的信号要声明为reg类型 寄存器定义 always @ (posedge CLK) //上升沿,下降沿用negedge表示,^_^ 需要记忆 begin Q <= D; end endm

关键字:

D触发器 Verilog

这次我们讲一讲如何入门学习硬件描述语言和数字逻辑电路;学习数字逻辑电路,我推荐的一本书就是--《数字设计-原理与实践》,其他的深入点可以看看《完整数字设计》;而对于硬件描述语言呢?有两个原则,一个是买书的原则,一个是看书的原则。首先,你必须买两类书,一类是语法书,平常使用的时候可以查一查某些语法;一类是,对语言的使用的讲解和使用的方法(如何书写RTL,如何设计电路,如何调试代码,使用仿真器等);我用过一年的VHDL和两年的Verilog;作为过来人,我想介绍一些比较好的书给入门者,避免大家走弯路。

关键字:

VHDL Verilog

这次我们讲一讲如何入门学习硬件描述语言和数字逻辑电路;学习数字逻辑电路,我推荐的一本书就是--《数字设计-原理与实践》,其他的深入点可以看看《完整数字设计》;而对于硬件描述语言呢?有两个原则,一个是买书的原则,一个是看书的原则。首先,你必须买两类书,一类是语法书,平常使用的时候可以查一查某些语法;一类是,对语言的使用的讲解和使用的方法(如何书写RTL,如何设计电路,如何调试代码,使用仿真器等);我用过一年的VHDL和两年的Verilog;作为过来人,我想介绍一些比较好的书给入门者,避免大家走弯路。

关键字:

Verilog RTL

IC设计业界目前正研究如何统合Verilog-AMS与IEEE 1800标准的SystemVerilog,或导入模拟混合信号(AMS)成为新的SystemVerilog-AMS标准。

目前四大验证语言标准有Verilog-A与Verilog-AMS、VHDL-AMS、SystemC-AMS、SystemVerilog-AMS。其中以SystemVerilog-AMS为最新标准,但仍需数年研究才能供业界使用。

根据智财标准设立组织Accellera官网,许多研究正如火如荼进行,聚焦新功能与产

关键字:

IC设计 Verilog

Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

浅析基于Modelsim FLI接口的协同仿真

介绍了如何利用modelsim提供的FLI(Foreign Langu

关键字:

HDL ASIC

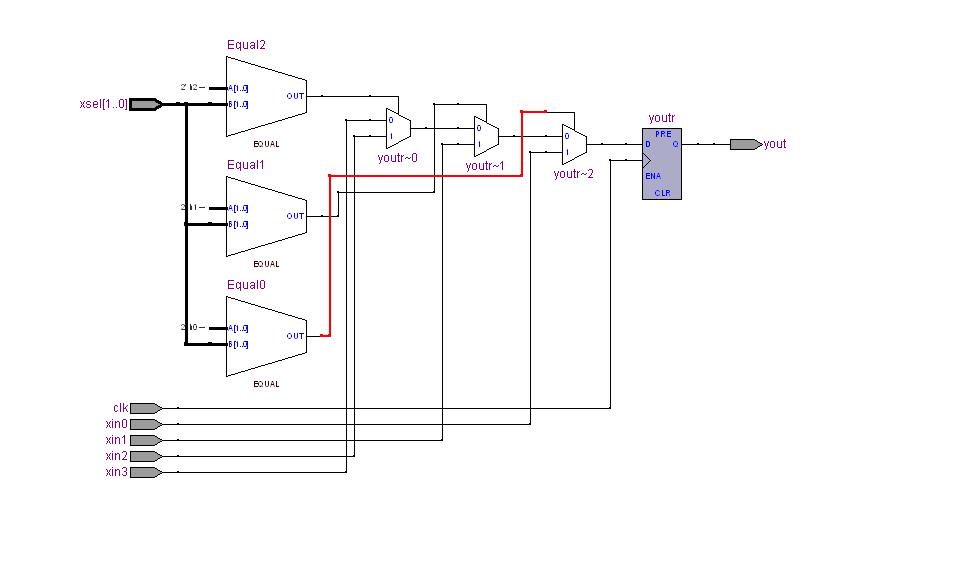

我们来做一个4选一的Mux的实验,首先是利用if…else语句来做,如下。

(由输入xsel来选择输出的路数xin0,xin1,xin2,xin3其一,输出yout)

Ex3:

input clk;

input xin0,xin1,xin2,xin3;

input[1:0] xsel;

output yout;

reg youtr;

always @ (posedge clk)

if(xsel == 2'b00) youtr <

关键字:

verilog RTL

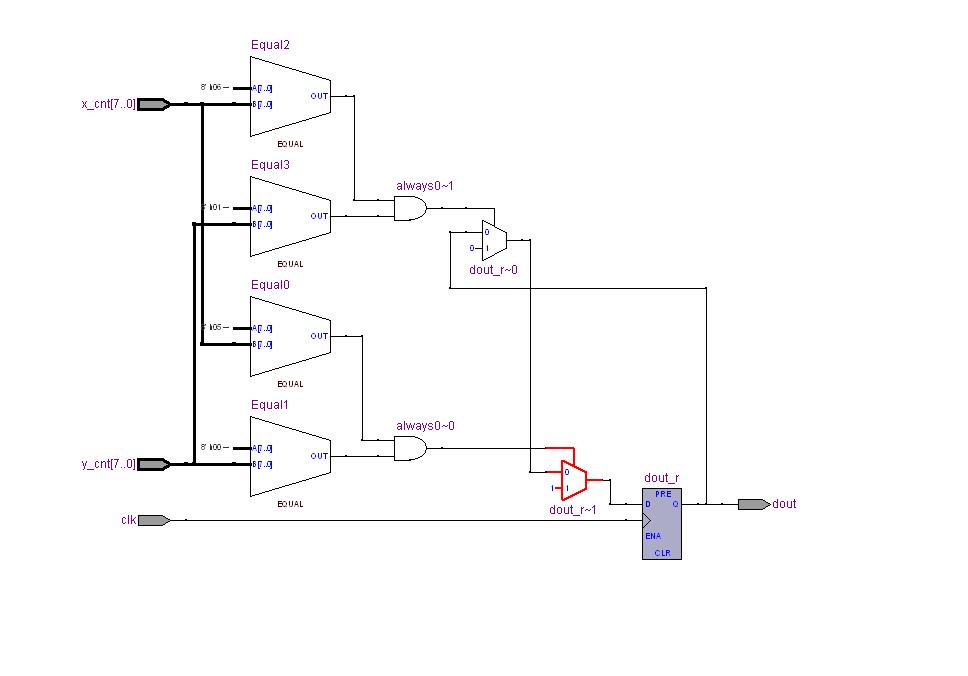

这次要说明的一个问题是我在做一个480*320液晶驱动的过程中遇到的,先看一个简单的对比,然后再讨论不迟。

这个程序是在我的液晶驱动设计中提取出来的。假设是x_cnt不断的增加,8bit的x_cnt加一个周期回到0后,y_cnt加1,如此循环,本意是要让下面的dout信号只有在x_cnt>=5 & y_cnt=0或者x_cnt<= 4,y_cnt=1这个区间内为1,其它时刻内为0。一般而言会有如下两种描述,前者是时序逻辑,后者是组合逻辑。当然除了下面两种编码风格外,还可以有很

关键字:

verilog RTL

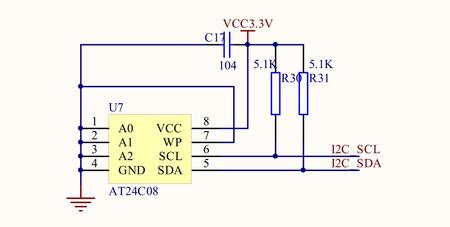

相信学过单片机的同学对I2C总线都不陌生吧,今天我们来学习怎么用verilog语言来实现它,并在FPGA学习版上显示。

i2c总线在近年来微电子通信控制领域广泛采用的一种新型的总线标准,他是同步通信的一种特殊方式,具有接口少,控制简单,器件封装形式小,通信速率高等优点。在主从通信中,可以有多个i2c总线器件同时接到i2c总线上,所有与i2c兼容的器件都有标准的接口,通过地址来识别通信对象,使他们可以经由i2c总线互相直接通信。

i2c总线由两条线控制,一条时钟线SCL,一条数据线SDA,这

关键字:

FPGA i2c verilog

一、关于HDL

1. HDL简介

HDL : Hardware Discription Language 硬件描述语言,即描述FPGA/CPLD内部逻辑门的工作状态,来实现一定电路。

随着EDA技术的发展,使用硬件语言设计PLD/FPGA成为一种趋势。目前硬件描述语言有VHDL、Verilog、Superlog、System C、Cynlib C++、C Level等。 各种语言有各种优势,根据业界应用而定。

2. VHDL和Verilog区别

在业界,VHDL和Veri

关键字:

FPGA Verilog

verilog-hdl介绍

您好,目前还没有人创建词条verilog-hdl!

欢迎您创建该词条,阐述对verilog-hdl的理解,并与今后在此搜索verilog-hdl的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473