基于CPLD的LCD1602显示系统设计与实现

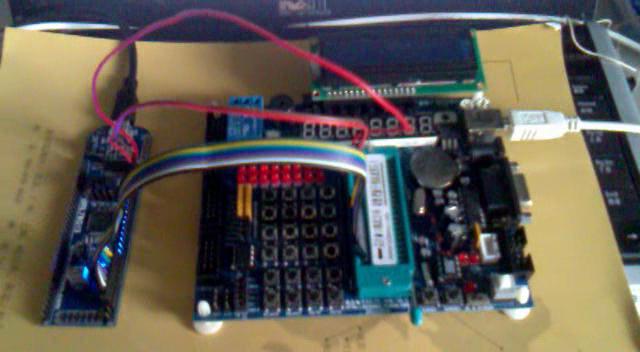

摘要:为了提高LCD1602显示效果,增强抗扰能力,文章基于TOP2812开发板,依据LCD1602操作时序要求,在开发板CPLD部分实现了LCD1602显示系统的设计。文中对LCD1602时序进行了详细分析,并在QuartusⅡ平台下采用Verilog HDL编写了test bench测试文件和驱动程序,经仿真和实际测试表明,显示效果较好,达到了设计要求。

本文引用地址:http://www.eepw.com.cn/article/201609/303571.htm关键词:CPLD;LCD1602;显示系统;时序;Vetilog HDL

随着技术的发展,社会数字化的程度显得越来越明显,集成电路在社会当中的应用也越来越广泛。传统的ASIC曾在数字领域扮演重要角色,虽种类繁多,但功能固定、管脚有限,应用范围也相对较窄,因此在一定程度上限制了人们对其的使用。如今,随着现场可编程技术的发展,FPGA及CPLD技术已不再是传统 ASCI技术领域的一个点缀与补充,其显然已成为电子应用领域广受欢迎的实用化技术,为数字系统的科研实验、样机试制、小批量产品的即时实现等提供了最佳途径。EPM240T100C5是Altera公司生产的MaxII系列CPLD,其功耗低、价格廉、配置灵活、资源丰富,具有较高的市场性价比,因而备受青睐。

在显示输出方面,目前主要采用3种方式,即:图形、数字或专用符号,在嵌入式领域,显示常采用LED、数码管及液晶显示器。前两种虽然实现简单,但显示内容不够丰富。LCD1602具有体积小、功耗低、显示容量大、接口简单,操作方便,能够显示字符、数字及符号等优点,因此被广泛应用于日常生活当中。

该文以EPM2405100C5为控制核心,在Quartus II平台下采用Verilog HDL编写LCD1602显示驱动程序,并生成相应目标文件,最终下载至目标芯片,实现LCD1602的显示设计功能。

1 实现原理

将EPM240T100C5的I/O口与LCD1602的数据管脚及控制管脚进行接口,利用Verilog HDL编写软件程序,使CPID输出满足LCD1602的操作时序。由于LCD1602属慢显示设备,而CPLD往往时钟频率较高,为此需要对CPLD主时钟进行分频,从而产生合适的时钟信号供LCD1602使用。在读/写数据时,需要对LCD1602的忙标志进行检测,只有在忙标志位为0的情况下,才能完成对数据或指令的读取与写入。此外,为方便对LCD1602模块进行操作,其内部控制器为该模块提供了11条控制指令,通过写入相应的控制指令,可定制该模块的显示模式。LCD1602为用户提供的存储空间分3部分:DDRAM、CGRAM和CGROM。DDRAM共有80个存储空间,对应屏幕的两行,每行40个,但每行可显示的地址只有16个,其他地址所写入的数据可通过移屏进行显示。CGRAM为用户自定义字符图形RAM,用户可以定制特定的图形。 CGROM为字符发生ROM,其内部已存储160个不同点阵字符图形,由于其编码与ASC II码基本一致,因此在进入写操作时,也可直接写入对应字符,如写8’h41,可显示字符A,直接写入“A”,也可达到同样的显示效果。

LCD1602的初始化主要用于完成字符显示模式、光标显示模式、写入数据后地址指针变化的设置、清屏及开显示等操作。该模块若要成功地被驱动,除了正确的初始化步骤以外,还必须依赖于准确的操作时序,因此分析其操作时序也就显得尤为重要。

2 时序分析

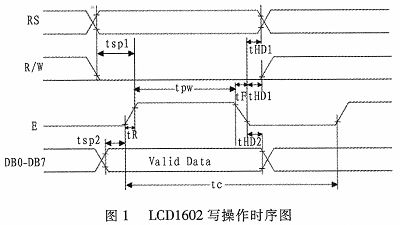

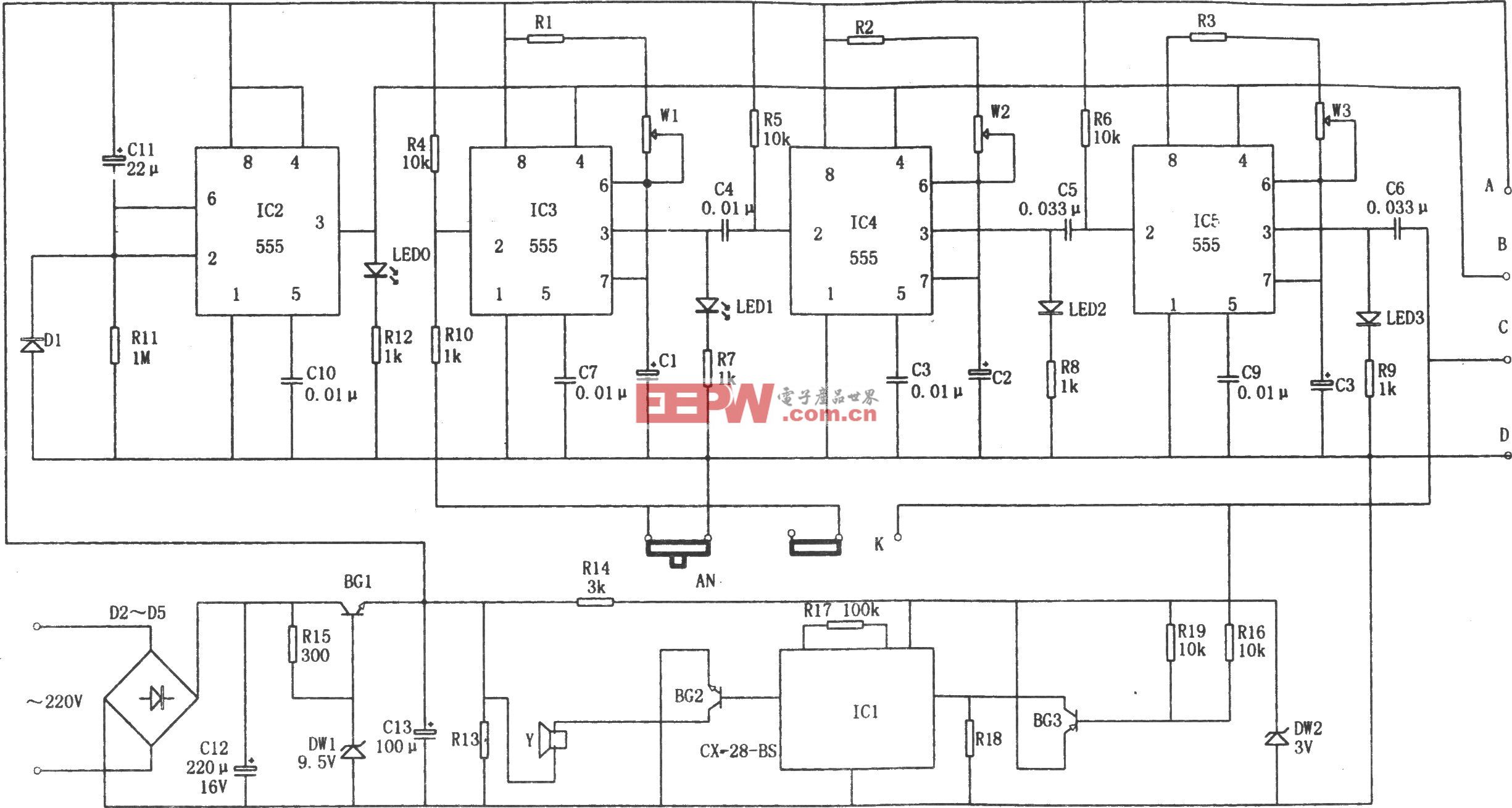

操作时序为IC芯片的工作提供了正确的节拍,如果节拍错了,那么芯片将不可能正常工作。LCD1602的写操作时序图如图1所示。

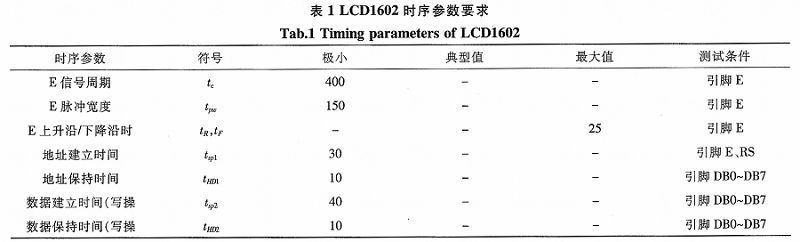

由图1可知,若要写入正确的数据,必须在E的上升沿到来之前建立RS及R/W电平,同时完成数据的写入操作,在E处于高电平期间,写入的数据才能有效。图 1中,tsp1即为RS、R/W的建立时间,tsp2为数据的建立时间,若要正确完成写入操作,必须使各建立时间满足时序要求。数据在E的高电平期间有效,即持续一个脉冲宽度tpw。图1中具体参数的时间要求如表1所示。

为方便建立E信号的波形,可取tpw=tc/2,即将E的波形设计为方波,只要保证tc>400 ns,则其高、低电平所维持的时间都将不小于200 ns,而如果将RS、R/W及数据变化的时间都取在E信号低电平的中间位置,则地址及数据的建立时间和地址及数据的保持时间都将大于100 ns,对比表1的时序参数要求,显然按这种方法设计出的时序是完全满足LCD1602写操作时序要求的。

因此,只需选取一个合适的tc,也就基本确定写操作时序了。由于LCD1602初始化时需要延时5 ms来完成对显示模式的设定,因此可选取5 ms作为tc的取值,从而简化显示模块的初始化操作。

3 软件实现

文中设计采用Verilog HDL实现,模块程序的接口如下所示:

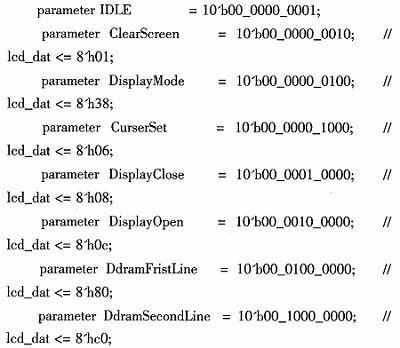

由于LCD1602初始化需要按特定步骤写入不同的控制指令,其可显示的数据地址在空间上是两个独立的固定区域,因此可借用有限状态机的设计思想进行设计系统。状态采用一位独热码进行编码。所定义状态如下:

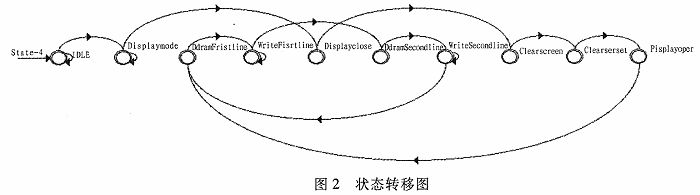

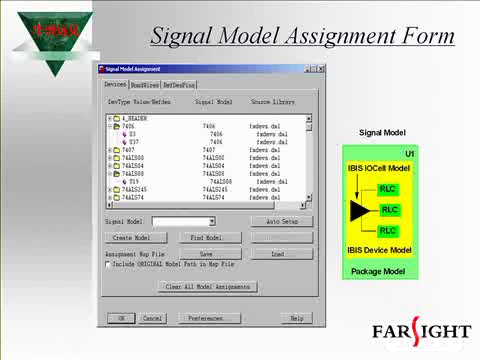

在QuartusⅡ平台下,经综合所得的状态转移关系如图2所示。

要想实现状态的转移,需构建LCD1602显示模块所必需的时钟,在时序分析过程中已确定将E信号的周期设计为5ms,而数据的写入以及RS、R/W电平的变化总是在E信号低电平的中间发生,因此可重新建立一个时钟,使其在该位置发生跳变,可以是上升沿也可以是下降沿,其周期与E信号周期相等,为便于设计,也将该时钟设计成脉宽为50%的方波信号。这里设E信号的时钟为lcd_en,在E信号低电平中间位置跳变的时钟为clkjlag。若选择 clk_flag的上升沿触发RS、R/W电平的改变及数据的写入操作,则显然clk_flag高电平要超前clk_div高电平90°。为得到相位上互差90°的两个时钟,可以通过对系统时钟分频,构建一个周期为2.5ms的时钟clk_div,使得clk_flag总是在clk_div的上升沿翻转,而lcd_en总是在clk_div的下降沿翻转,由此即可得到相位上互差90°的两个时钟信号了。由于主时钟为30 Mhz,因此需对其进行37 500分频,即可得到周期为2.5 ms的clk _div。其软件实现如下:

评论