- 双数据速率(DDR)接口在时钟信号的上升沿和下降沿传送数据,这种方法已经用来实现DDR、SDRAM、微处理器前端总线、Ultra-3 SCSI、AGP总线等的通信链路。在每个周期中,数据在时钟的上升沿和下降沿采样,最高数据传输速率一般是时钟频率的2倍。

- 关键字:

DDR 微处理器 数据传输

- 安捷伦科技公司(NYSE:A)日前宣布为其屡获殊荣的 Infiniium 90000 X 系列示波器增添业界最高性能的混合信号示波器(MSO)功能。安捷伦不但推出了 6 种最新 MSO 型号,同时发布了13-GHz 带宽的DSO 和 DSA 型号,进一步扩展了 X 系列示波器。

- 关键字:

安捷伦 示波器 DDR

- “帧像”技术是康佳平板电视在图象显示领域的革命性突破,“帧像”技术的基本原理是在刷新频率为120HZ的屏幕...

- 关键字:

DDR 平板电视 帧像技术

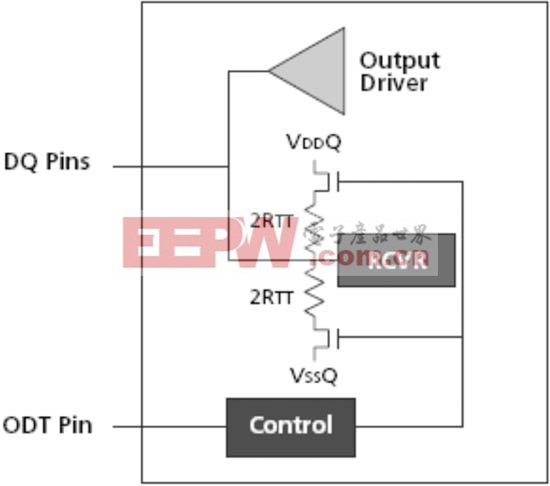

- 摘要 本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中

- 关键字:

DDR3 DDR 800 PCB

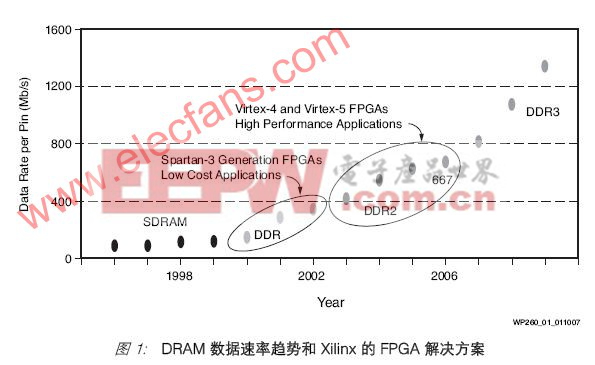

- 1 引言在高速信号处理系统中, 需要缓存高速、大量的数据, 存储器的选择与应用已成为系统实现的关键所在。DDR SDRAM是一种高速CMOS、动态随机访问存储器, 它采用双倍数据速率结构来完成高速操作。SDR SDRAM一个时钟周

- 关键字:

Xilinx SDRAM FPGA DDR

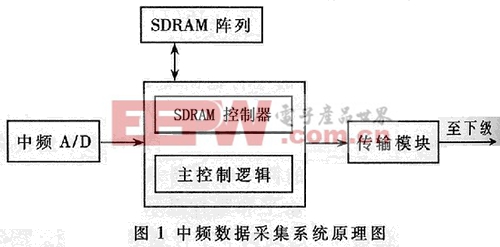

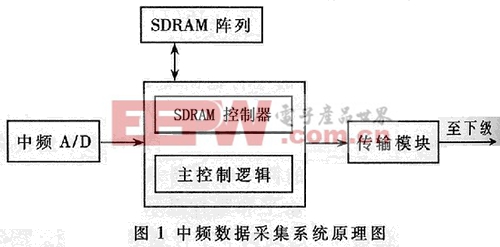

- 实现数据的高速大容量存储是数据采集系统中的一项关键技术。本设计采用Altera 公司Cyclone系列的FPGA 完成了对DDR SDRAM 的控制,以状态机来描述对DDR SDRAM 的各种时序操作,设计了DDR SDRAM 的数据与命令接口。用控

- 关键字:

SDRAM FPGA DDR 控制器

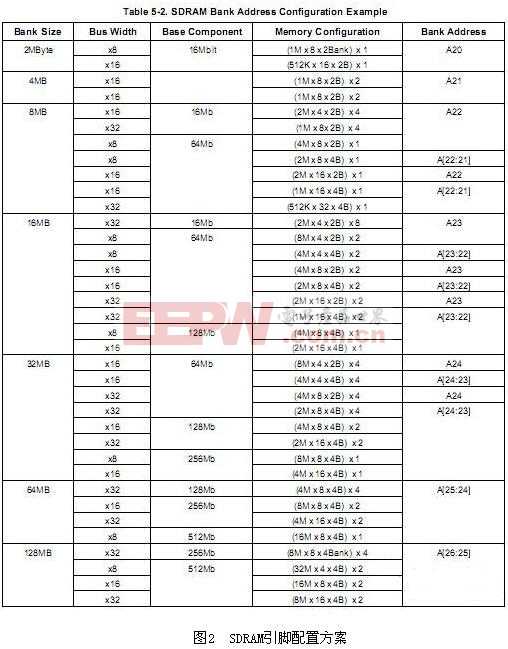

- 在高速实时或者非实时信号处理系统当中,使用大容量存储器实现数据缓存是一个必不可少的环节,也是系统实现中的重点和难点之一。SDRAM(同步动态随机访问存储器)具有价格低廉、密度高、数据读写速度快的优点,从而成

- 关键字:

实现 控制器 SDRAM VHDL 基于

- 全球领先的电子器件和系统设计、验证和制造软件及知识产权(IP)供应商新思科技公司(Synopsys, Inc., 纳斯达克股票市场代码:SNPS)日前宣布:其DesignWare DDR接口IP产品组合已经实现扩充,以使其包括了对基于新兴的DDR4标准的下一代SDRAM。通过在一个单内核中就实现对DDR4、DDR3以及LPDDR2/3的支持,DesignWare DDR解决方案使设计师能够在相同的系统级芯片(SoC)中,实现与高性能或者低功耗SDRAM的连接,它已经成为诸如用于智能手机和平板电脑的应用处理

- 关键字:

Synopsys SDRAM

- DR2(Double Data Rate 2,两倍数据速率,版本2) SDRAM,是由JEDEC标准组织开发的基于DDR SDRAM的升级存储技术。 相对于DDR SDRAM,虽然其仍然保持了一个时钟周期完成两次数据传输的特性,但DDR2 SDRAM在数据传输率、

- 关键字:

CPU 硬件 设计 MPC8548 基于 SDRAM 介绍 及其 DDR2

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

DSP 存储系统 SDRAM

- DDR2简介从1998年的PC100到今天的DDR3,内存技术同CPU前端总线一道经历着速度的提升及带宽的扩展。虽然DDR3在当今已经量产与使用,DDR2在实际上还担任着内存业界应用最广泛最成熟的中流砥柱的角色。DDR2在DDR的基础上

- 关键字:

DDR2 DDR 测试 力科

- 存储器是容量数据处理电路的重要组成部分。随着数据处理技术的进一步发展,对于存储器的容量和性能提出了越来 ...

- 关键字:

多路读写 SDRAM 数据处理

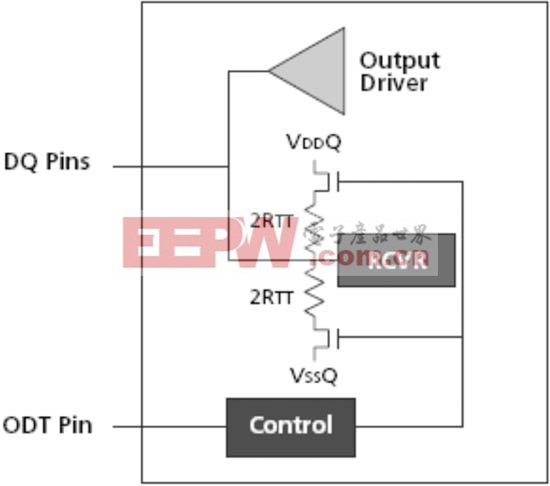

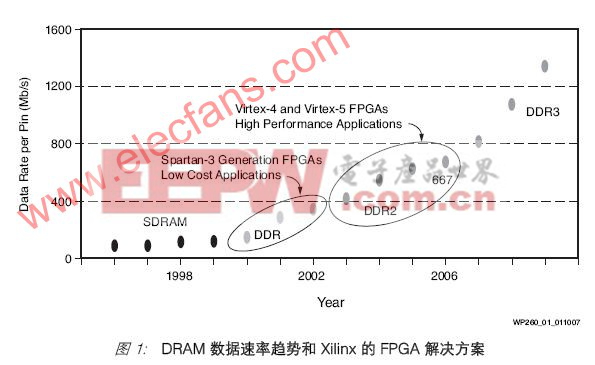

- 采用Xilinx 和FPGA的DDR2 SDRAM存储器接口控制器的设计,本白皮书讨论各种存储器接口控制器设计所面临的挑战和 Xilinx 的解决方案,同时也说明如何使用 Xilinx软件工具和经过硬件验证的参考设计来为您自己的应用(从低成本的 DDR SDRAM 应用到像 667 Mb/sDDR2 SDRAM 这样的更

- 关键字:

接口 控制器 设计 存储器 SDRAM Xilinx FPGA DDR2 采用

- 摘要:充分利用DDR2 SDRAM速度快、FLASH掉电不消失、MATLAB/Simulink易产生矢量信号的特点,以FPGA为逻辑时序控制器,设计并实现了一种灵活、简单、低成本的矢量信号发生器。本文以产生3载波WCDMA为例,详细介绍了矢量信号发生器的设计方案与实现过程,使用Verilog HDL描述并实现了DDR2 SDRAM的时序控制和FPGA的逻辑控制。

- 关键字:

DDR2 SDRAM FLASH 201205

- DDR是双倍数据速率的SDRAM内存,如今大多数计算机系统、服务器产品的主流存储器技术,并且不断向嵌入式系统应用领域渗透。孰不知,随着iPhone等大牌智能手机的采纳,DDR内存俨然成为智能手机转变的方向之一,例如韩国

- 关键字:

DDR 测试技术 分析

ref-ddr-sdram介绍

您好,目前还没有人创建词条ref-ddr-sdram!

欢迎您创建该词条,阐述对ref-ddr-sdram的理解,并与今后在此搜索ref-ddr-sdram的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473