FIR数字滤波的FPGA实现

3.2.2将模型转成VHDL文件

本文引用地址:https://www.eepw.com.cn/article/87259.htmSimulink仿真完成后就可以在硬件上实现设计,以获得针对特定FPGA芯片的VHDL代码。

用SignalCompiler对模型进行分析,检查其正确性。选择对应的器件系列并对SignalCompiler 进行相应的设置,把MDL文件转换成VHDL文件。

3.2.2 ModelSim功能仿真

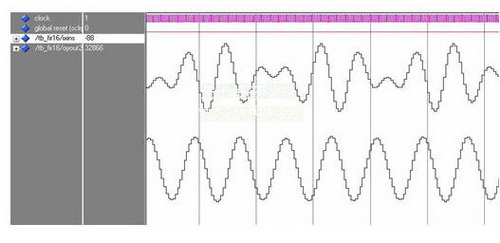

Simulink算法级、系统级仿真后还要用ModelSim对生成的RTL级VHDL代码进行功能仿真。仿真波形见图3。

图3 ModelSim仿真波形

Fig.3 Simulation wave shape of ModelSim

3.2.3 QuartusII时序仿真

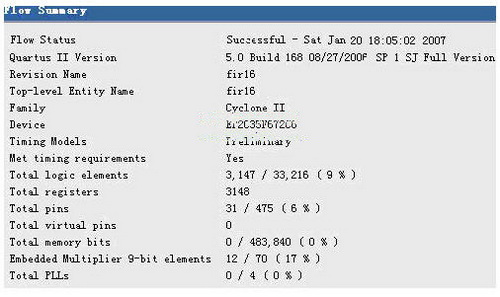

RTL级仿真完成后还要进行门级时序仿真。SignalCompiler已将Matlab上的仿真信息转变为可用与QuartusII 进行时序仿真的激励信息及相关的仿真文件,因此可以很容易地完成此项仿真任务[2]。

QuartusII仿真编译结果 显示了仿真编译的各项参数,由图4可得FPGA的器件型号、逻辑元件及引脚的使用数目和占用资源百分比等情况。

图4 QuartusII仿真编译结果

Fig.4 the Result of Compilation & Simulation

4 硬件实现

经过Matlab、ModelSim、QuartusII联合仿真验证后,最后把VHDL烧写到基于Cyclone II EP2C35F672C6 FPGA 芯片的开发板中,完成FIR滤波器在FPGA上的硬件实现。

5 结论

本文通过利用DSP Builder设计建模电子模块来代替编写VHDL 程序,设计效率大为提高。然后通过Matlab的Simulink环境的图形化仿真验证功能配合ModelSim RTL级仿真与QuartusII门级时序仿真功能对设计的程序功能进行全面验证,确保功能正确。通过SignalCompiler转换为VHDL语言实现,还可以在不同公司的FPGA器件之间移植,给设计带来很大的灵活性。同时,参数化结构设计,可根据情况调整设计规模在FPGA上实现FIR数字滤波。

FIR滤波器以其优越的性能在数字信号处理领域中占有很重要的地位。利用FPGA实现FIR数字滤波器,具有实时性、灵活性以及执行速度快等特点,大大提高了滤波器设计、计算、调试的速度。

本文作者创新点,抛弃传统的通用数字滤波集成电路,选用FPGA来实现FIR数字滤波。用FPGA实现数字滤波具有灵活性强、精度高、处理速度快、成本低等多种特点,提高了工作效率,降低了生产成本,有一定的市场前景。

参考文献:

[1] 潘松,黄继业,曾毓.SOPC技术实用教程[M].北京:清华大学出版社,2005

[2]于枫, 张丽英, 廖宗建.ALTERA可编程逻辑器件应用技术[M].北京:科学出版社,2004

[3] (日)谷萩隆嗣.数字滤波器与信号处理[M].北京:科学出版社,2003

[4] 赵文兵,杨建宁. FIR滤波器的FPGA实现及其仿真研究[J].微计算机信息,2005,21-7:108-109

江苏省科技攻关重大项目(工业部分),项目编号:BE2006090

评论