FIR数字滤波的FPGA实现

摘要: 随着数字技术的发展,数字滤波器的功能越来越受到人们的注意和广泛应用,它有精度高、灵活性大等突出特点。FIR数字滤波具有稳定性高,严格的线性相位,能用FFT算法实现等特点。通过FPGA实现FIR数字滤波具有实时性高、处理速度快、精度高的特点。文章先通过Matlab DSP Builder 设计出FIR滤波器模型,然后利用Simulink进行模型仿真,再用ModelSim进行功能仿真,最后用Quartus II进行时序仿真。仿真结束后下载到选定的FPGA上,在FGPA上实现FIR数字滤波。

关键词:数字滤波;FIR滤波器;FPGA; Matlab

0 引言

随着科技的发展,数字信号处理在通信、自动控制、雷达、军事、航空航天、医疗、家用电器等众多领域得到了广泛的应用。而在数字信号处理的应用中,数字滤波器是相当重要的一部分。其中无限冲击响应(IIR)数字滤波器和有限冲击响应(FIR)数字滤波器是目前人们使用较多的两种。与IIR数字滤波器相比较,FIR数字滤波器具有稳定性高,速度快的特点。

FIR数字滤波器可以通过软件或者硬件来实现。所谓软件实现就是利用通用计算机实现。而硬件实现就是设计专门的数字滤波硬件,有以下几种实现方法,1)使用单片通用数字滤波器集成电路;2)采用DSP器件实现;3)采用可编程逻辑器件实现[4]。比较普遍的有DSP、ASIC、FPGA等。与FPGA相比较,DSP的顺序执行使得其速度较慢,而ASIC的设计成本又比较高,所以用FPGA实现FIR数字滤波,具有实时性强、灵活性高、处理速度快以及小批量生产成本低等特点。

1 FIR数字滤波器设计要求与结构选择

FIR滤波器实现的基本结构有:直接型、级联型、频率抽样型、快速卷积型结构几种[3],这里以直接型为例。设计一个16阶的FIR低通滤波器(h(0)=0),采样频率Fs=200Hz,滤波器截止频率Fc=40Hz,输入序列位宽为9位(最高位为符号位)。

2 FPGA的选择

考虑到价格以及芯片内部嵌入式乘法器对数字信号处理的支持性,这里选用的是Altera公司出品的低端FPGA芯片Cyclone II EP2C35F672C6,它主要由逻辑阵列、M4K存储器块、数字[1]锁相环、嵌入式乘法器几部分组成。

3 FIR设计软件平台

3.1 基于Matlab和DSP Builder的模型设计

3.1.1 Matlab

Matlab可以进行科学计算、图像处理、声音处理等,有良好的用户界面和帮助功能。其中的Simulink软件包可以对动态系统进行建模、仿真和分析,支持连续、离散及混合的线性、非线性系统,同时支持具有多种采样频率的系统。在Simulink环境中,在模型窗口中可以用鼠标直观地“画”出系统模型,然后直接进行仿真。采用Scope模块和其它的画图模块,还可以在进行仿真的同时看到仿真结果[1]。

3.1.2 DSP Builder

DSP Builder 是一种系统级的专门设计DSP处理器及系统的工具,它架构在多个软件工具如Matlab、QuartusII、Synplify之上,把系统级和RTL级的设计工具连接起来,最大程度地发挥多种工具的优势。DSP Builder可以帮助设计者完成基于FPGA的DSP系统设计,它以Matlab中Simulink 的工具箱出现,可以在Simulink 中进行图形化设计和仿真,同时通过Signal Compiler可以把设计文件转成相应的硬件描述语言设计文件,以及用于控制综合与编译的TCL脚本[1]。

3.1.3 基于Matlab、DSP Builder的FIR数字滤波器设计

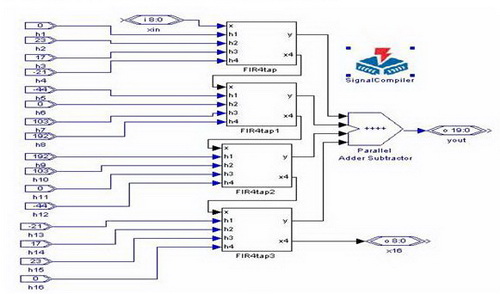

利用直接型滤波器可以级联的特性,我们可以调用4个4阶FIR滤波器来实现一个16阶的低通滤波器。如图1所示,其中每个firtap都是一个4阶FIR滤波器。

图1 直接I型16阶FIR滤波器

Fig.1 16-step Direct I Type FIR Digital Filter

利用Matlab里的滤波器设计工具获得各种滤波器设计参数,选择滤波器类型为低通FIR,设计方法为窗口法,15阶,Kaiser窗,Beta=0.5,FS为200Hz,FC为40Hz。利用FDATool分析所设计出的滤波器的幅频、相频特性,冲激、阶跃响应,零极点等,导出滤波器系数并对其进行量化及优化,得到整型的滤波器参数并分别填入到FIR滤波器模型中,完成设计。

3.2 模型仿真调试

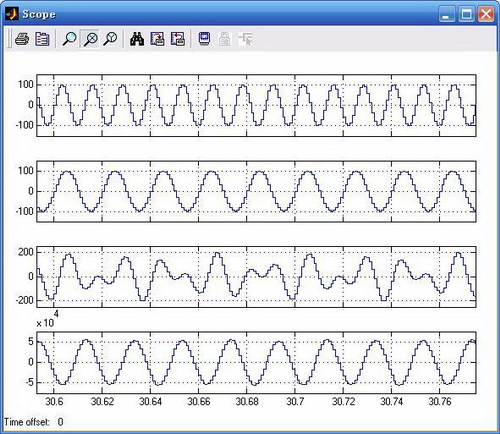

3.2.1 Simulink 模型仿真

模型设计好后,即可在Simulink中进行算法级、系统级仿真验证。在模型的输入端加入一个叠加信号,验证FIR低通滤波器模型设计的正确性。如图2所示,自上而下四个波形分别是58Hz、30Hz输入波形,二者的混合波形,输出波形。可见滤波器模型正确。

图2 模型仿真结果

Fig.2 the Result of Model Compilation

评论