基于FPGA的中高频感应电炉控制电路设计方案

1 引 言

本文引用地址:https://www.eepw.com.cn/article/84779.htm中高频感应炉是利用电磁感应原理加热和溶化金属的,这种方式是一种较理想的加热工艺,已经广泛应用于金属熔炼、焊接、表面淬火等加工和热处理过程。中高频电炉的负载是由感应圈和被加热的金属工件组成,为了降低无功功率,需要用串联或并联电容的方式来补偿无功功率,使整个电路中形成中高频的LC振荡。维持这样较恒定的频率振荡,金属内部将形成涡流而发热,从而达到加热和熔化金属的目的。传统的控制电路主要采用分离元件的模数混合电路,控制精度低,容易产生噪声问题。

本文将提出一种基于FPGA片上可编程技术实现数字化控制方案,代替传统的数模混合电路,从而可提高其控制的可靠性,稳定性,同时也可以提高系统集成度并降低噪声干扰。设计主要采用VerilogHDL硬件描述语言实现模块化的设计,构成片上可编程系统,用QuartusⅡ7.0软件模拟仿真,并进行了模块实际验证。

2 中频感应电炉的控制电路工作原理

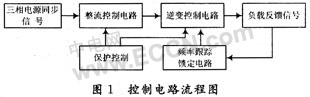

中高频感应电炉控制电路主要由以下几个部分组成:三相电源整流控制电路,逆变控制电路及工作频率的跟踪锁定控制电路,如图1所示。

3设计方案的提出

传统的中高频电炉采用分散式模块设计,而大量采用分离原件,如556,计数器来实现整流脉冲的控制,CD4046来实现频率跟踪,保护电路则主要使用大量集成运算放大器LM324。这种设计造成整个控制电路繁琐,难于调整,易出现问题。本文提出基于Altera FPGA技术,控制电路实现数字化的片上系统。从原理上来看,控制电路的核心主要是整流脉冲输出和逆变频率的跟踪,如果在FPGA上实现,必须解决这两个模块的设计。首先,整流脉冲输出是个时序问题,通过硬件描述语言可以实现。其次,逆变频率的跟踪可以利用全数字锁相环来实现。最后,这些设计模块可以集成到一片FPGA上。从原理上讲,我们提出的方案是可性的。

4 三相桥式全控整流原理及模块设计

4.1 三相桥式全控整流原理

三相桥式全控整流电路如图2所示,6只整流元件全部采用可控硅(共阳极组的元件在各自的电源电压为正半周期时导通,而共阴极组的元件则在其电源电压负半周期时导通)。所有可控硅元件均靠触发换流,且控制角α相同。6只可控硅的导通条件是相同的,即都必须在其阳极承受正向电压期间在控制极上加触发脉冲。为使全控桥能正常工作,形成电流通路,必须使共阳极组和共阴极组的元件在任一瞬间各有1只处于导通状态(在换流期间则有3只元件导通,其中2只处于换流状态)。触发脉冲必须适应三相桥式全控整流电路的要求,当选择采用双脉冲触发时,即触发脉冲信号源同时发出两个脉冲,如果一个触发脉冲加至共阴极组的一个元件,则另一触发脉冲加至共阳极组中的前一个元件。因此,用双窄脉冲触发,在一个周期中对每一只可控硅触发两次,两次脉冲中间的间隔为60°。共阳极可控硅依次导通,他们的触发脉冲间隔依次有120°的相位差;同理,共阴极可控硅的触发脉冲也依次相差120°。相位移相触发就是通过改变晶闸管每周期导通的起始点即触发延迟角α的大小,达到改变输出电压、功率的目的。通过改变控制角α的大小,可以改变整流桥输出直流平均电压的大小。数字移相触发是把算出的控制角α折算成对应的延时t=aT/360(T为晶闸管交流电源周期),t乘计数时钟频率则得计数脉冲数。

4.2 FPGA软件编程实现可控硅双脉冲

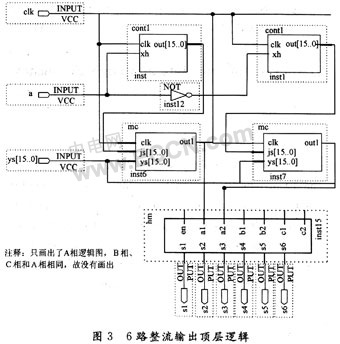

计数脉冲频率为FPGA芯片的全局时钟频率。三相电压信号通过光电耦合器变换成为A,B,C,均为50 Hz占空比50%的方波信号,所产生的双触发脉冲的宽度可通过程序中定义的变量j来进行调整。程序主要设计将实现两个功能:对计数脉冲数据ys的锁存和计数产生触发脉冲。更新ys就可以达到相位移动。电压A,B,C之间相位相差120°,对每相电压均设有两个计数器,分别对其正相和负相进行计数,共6个计数器count1,count2,count3,count4,count5,count6。在A为高电平时count1开始计数,当i

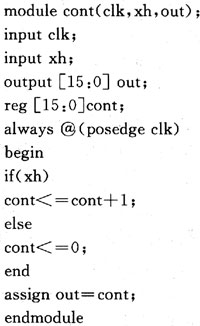

4.3 部分VerilogHDL程序代码

计数器模块设计代码如下:

4.4仿真的结果

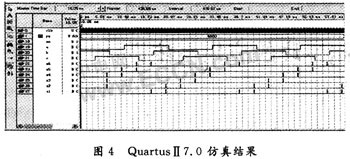

计数脉冲数i变化时,α角也有相应的变化。所得6路触发脉冲s1,s2,s3,s4,s5,s6保证同时触发全控整流桥中相邻的两个可控硅,其中一个在共阳极组中,一个在共阴极组中。仿真结果如图4所示。

5频率跟踪及逆变脉冲原理及模块设计

通常感应加热电源利用锁相环电路控制逆变器,一方面利用锁相环电路实现逆变器的输出电压自动跟踪负载的电流信号,使逆变器工作在准谐振状态或谐振状态,保证整个加热过程中负载呈现一定的性质或负载在高功率因数下运行,功率开关器件损耗也就减小了,另一方面保证电源在工件热状态下能输出额定功率,而工件为冷态时又不会过载,即提高了电源的负载适应性。由此可见锁相环电路在感应加热电源中有着很重要的作用。

5.1数字锁相环的工作原理

数字锁相环路(DPLL)的基本结构如图5所示。主要由鉴相器DPD、数字环路滤波器DLF、脉冲加减电路(数控振荡器DCO)和分频器(可控变模N)四部分构成。脉冲加减电路的时钟分别为2Nfc,fc为环路中心频率。DPLL是一种相位反馈控制系统,他根据输入信号fin与输出信号,fout之间的相位误差(超前还是滞后),误差信号在数字环路滤波器DLF中进行平滑滤波,并生成控制DCO动作的控制信号DCS,DCO根据控制信号给出的指令,调节内部高速振荡器的振荡频率,通过连续不断的反馈调节,使其输出fout的频率跟踪输入数据fin的频率。

由于FPGA芯片内集成的锁相环大部分都是应用在通信领域,所以锁相频率非常高,并不适合感应加热电源的需要。根据数字锁相环原理用硬件描述语言设计锁相环。考虑到中频电炉随着负载的变化,工作频率也在不断的变化,就要求锁相环的锁频范围比较宽泛。如图5所示锁相环输出频率为fout=Fd/N,要想改变锁相环输出的频率大小,就要改变N分频器取值,使N分频器能够跟随负载进行动态的调整,就可以实现锁相范围的最大化。具体说来,由图5可以看出频率,fout与fc是对应的关系。假设取2Nfc为系统时钟,则fout的频率等价于系统时钟的1/N,考虑到数控振荡器相当于二分频,而设计的分频器本身也是个二分频,若取N为fin的高电平在系统时钟下的计数值的一半,那么从频率上看fout与fin的频率相等。随后通过环路滤波器的增减脉冲,送给数控振荡器,就可以实现相位的不断地调整,最终达到锁相的目的。

5.2程序模块代码设计

计数器模块设计代码如下:

5.3试验仿真结果分析

整个系统进行完软硬件调试之后就可以对该锁相环进行测试和验证,使用QuartusⅡ软件中集成的仿真器进行测试,测试后的波形图如图6所示。

其中1 MHz是整个系统的时钟信号,提供系统时钟。Fin是锁相环的输入信号,Fout就是锁相环的输出信号。可以看到,在经过一段时钟周期之后,输出信号就逐渐锁定了。

经过实际检验,该锁相环的锁相范围的频率可以达到从1~100 kHz,这样就能够应用于中频感应加热电路,从而解决了中低频信号不能够使用片内数字锁相环,以及重新设计数字锁相环这类繁琐的工作。

6结 语

软件设计方面采用Altera公司推出的综合开发平台QuartusⅡ7.0。他集成了Altera的FPGA/CPLD开发流程中所涉及的所有工具和第三方软件接口。通过使用此综合开发工具,设计者可以创建、组织和管理自己的设计。在具体的设计方面采用了自顶向下,模块化的设计方法,这符合人们先整体后局部的思维习惯,并方便进行局部模块的修改,而不会影响其他的模块,利用率高。本设计简单易用,为中频感应加热电炉控制提供了一种可行的片上集成方案。系统模块可以根据实际需要进行改动,可修改性强,易于系统控制电路的升级。本论文未涉及到系统保护电路的需求,可以通过改动或增加系统模块来实现。

DIY机械键盘相关社区:机械键盘DIY

电路相关文章:电路分析基础

fpga相关文章:fpga是什么

可控硅相关文章:可控硅工作原理

分频器相关文章:分频器原理 电流传感器相关文章:电流传感器原理 鉴相器相关文章:鉴相器原理 电子负载相关文章:电子负载原理 脉冲点火器相关文章:脉冲点火器原理 锁相环相关文章:锁相环原理

评论