DM642平台多路视频处理系统的实时性分析

引 言

本文引用地址:https://www.eepw.com.cn/article/82488.htm视频合成技术是图像处理方面的一个重要应用,它将一个图像的多个状态或者多幅不同图像进行合成,来实现虚拟面板、图像叠加、模拟场景、图像优化等效果。多路视频合成显示技术是将通过多个途径(如摄像机、PC机、网络等),采集而来的多路视频信号进行处理,并按照实际所需进行显示。

选择适当的核心处理芯片,对数据量大、实时性高的视频信号处理来说,是首要考虑的问题。美国TI公司推出的针对视频和图像解决方案的TMS320DM642型高性能数字媒体处理器,是TI公司C6000系列中一款基于DaVinci技术的DSP,其核心是C6416型高性能数字信号处理器,具有极强的处理能力、高度的灵活性和可编程性,同时外围集成了非常完整的音频、视频和网络通信等设备及接口,特别适用于机器视觉、医学成像、网络视频监控、数字广播,以及基于数字视频/图像处理的消费类电子产品等高速DSP应用领域。本设计利用这一处理器,实现了一套4路、高清晰度的图像显示系统:所采集的视频信号是4路高清晰度视频图像——3路1 024×768@60Hz的VGA视频信号、1路768×5766@25帧(PAL制式)的S-Video视频信号;视频输出为单屏幕多窗口,分辨率为1024×768的RGB视频图像;刷新频率为60帧/s。

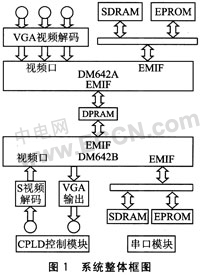

系统的硬件部分主要包括:视频输入解码模块、DSP核心处理模块、视频输出接口模块、串口通信模块、CPLD控制模块,系统整体框图如图1所示。

1 系统整体描述

系统通过视频转换芯片AIT2138和SAA7110来采集视频信号,采用2片DM642(分别记DM642A和DM642B)并联,其中主算法的实现在DM642B中进行。DM642A的3个视频端口全部用于视频采集,采集3路RGB信号。采集后存到DM642A的外部存储器SDRAM1,等DM642B执行算法时,DM642A按照需要将数据传至DM642B。处理完之后数据经DM642B视频口输出为RGB格式,并由ADV7125完成数模转化,输出至VGA接口。系统采用Altera公司的EPM7128S CPLD来完成逻辑产牛和系统控制,采用Philips公司51系列单片机P89C668通过串口与PC机通信,方便地完成显示模式的切换。

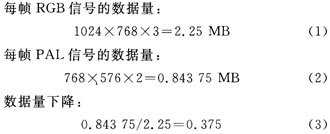

2 数据通信量分析

鉴于DM642视频端口的传输能力,3路1024×768@60 Hz的RGB信号的数据量过大,无法实时处理。所以将其通过AIT2138(该芯片支持NTSC和PAL两种制式输出)转化成768×576@25 Hz的PAL电视信号。电视信号再经过SAA7110转化成16位的数字Y/C分离信号。所以每帧图像传至DSP视频输入口时的数据有显著下降。公式如下:

即下降到原始数据量的3/8。简化了后边的数据处理过程。

3 系统的实时性分析

先预定系统的系统时钟频率为133 MHz(按照DM642硬件说明书上的建议,此时DSP外部存储器应选用6 ns级)。DSP数据总线宽度64位,每帧图像从DSP的视频通道进入二级缓存L2的时间为:

0.843 75 MB/64×133 MHz=0.8 ms (4)

因为DM642A没有数据的取舍权,所以3路数据要全部存入SDRAM。实际所需时间应为:

0.8×3=2.4 ms (5)

这一步必须计算成3帧图像的时间。因为只有3路各到1帧图像时,才能对其数据选择,满足后边选定窗口大小的需求。

至此,数据传输都是按照既定窗口大小的数据量进行传输的。也就是说,对应要显示的合成后的1帧图像,DM642A向DM642B传输的数据不大于1帧:4个窗口均匀显示时,DM642A到DM642B传输的数据大小为3/4帧,DM642A的某一路全屏显示时传输为1帧,当DM642B的S-Video全屏显示时,不用传输。

以下是数据流经各个部分的时间估算:

DM642A上的3路

①视频口→内存 2.4 ms

②内存→SDRAM 12.4 ms

③SDRAM1→内存 <0.8 ms

④内存→DPRAM <0.8 ms

⑤DPRAM→DM642B <0.8 ms

DM642B上的1路

⑥视频口→内存 0.8 ms

⑦内存→SDRAM2 0.8 ms

③SDRAM1→内存 <0.8 ms

⑨内存→视频输出端口 0.8 ms

不考虑流水,总耗时为各个时间之和:

①+②+③+④+⑤+⑥+⑦+⑧+⑨=1004 ms

上述过程中可以同时进行的有:

①和⑥、②和⑦、③和⑧、④和⑤。

这样就实现了一定程度的流水。由此得出,从系统开始采集原始数据,到1帧合成好的图像显示到屏幕上所需时间为:

①+②+③+④+⑨=7.2 ms

也就是说,系统处理能力较强,每秒能处理的电视图像数目可以满足实时显示的需要。

4 两片DSP之间的连接方式

EMIF(外部存储器接口)方式连接。这种方式是采用一个DPRAM作为2片DSP的公用外部存储器。在DM642要执行算法时,DM642A将组织好的数据以访问外部存储器的方式存到DPRAM,然后DM642B同样以访问外部存储器的方式将所需数据取走。此时2片之间是并联关系,因为DM642B不能对DM642A进行传输数据时机的控制,所以需要通过专门的控制逻辑来协调2片DSP之间的配合。这种方式数据传输宽度为64位,需要与其他连接到EMIF数据总线上的外部存储器或I/O设备分时复用。

5 DM642视频通道的说明

DM642是一款基于TI DaVinci技术的专门用于视频多媒体处理的芯片。它集成了3个视频口,分别为VP0、VP1、VP2。每个视频口都可以作为一个视频捕捉口、视频显示口或是传输数据流输人接口。

每个视频口有A和B两个通道,两个通道共用一个5 120字节的捕获/显示缓存。对于整个视频口,要么设置成视频捕捉口,要么设置成视频显示口。也就是说,A、B两个通道必须一致,同为输入或输出。不管是BT656、Y/C、Raw video,或者是传输数据流格式,视频口都有独立的数据通道来控制视频输入或输出数据的解析和格式化。

对于视频捕捉操作,视频口既可以以双通道的方式对两路8/10位的BT656视频或Raw video格式捕捉;也可以单通道的方式对8/10位的BT656、8/10位Raw video图像,16/20位Y/C,16/20位Raw video图像或者是8位的传输流进行捕捉。

对于视频显示操作,单通道时的视频口用法和上边提到的捕捉时相同。作为双通道时,可以显示连接到相同时序的双通道8/10位原始视频。单通道时通道B闲置不用。

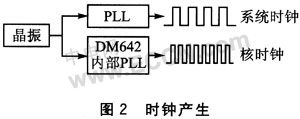

6 时钟频率设计

系统时钟(存储器、DSP I/O口时钟)采用133 MHz,由外部晶振通过锁相环倍频提供。DM642核时钟采用600 MHz,由与系统时钟同源的外部晶振通过内部倍频得到,如图2所示。

此外视频编解码芯片根据自身制式特性单独处理。输入视频的同步信号,由输入RGB视频的同步信号通过处理得到。

7 两片DSP的步调协调

时钟可共用。但是由于数据传输途径的差别,DM642B捕捉的S-video做好处理前准备的时间要少于DM642A过来的RGB视频。

系统启动后,当DM642A的数据执行到③的时候,DM642B开始捕捉S-video,从⑥开始进行。这样,对以每次DM642A采集3路各1帧图像时,DM642B应等待4.8ms再开始要采集与之对应的1帧S-video。

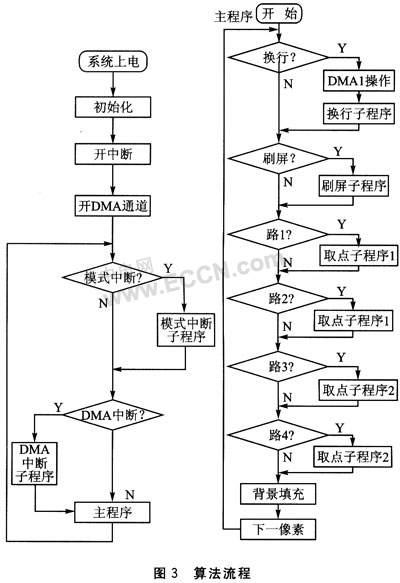

8 算法流程和执行

算法流程如图3所示。

鉴于本部分不是该文重点,故在此只作简单说明。该算法设计的出发点都是由DM642B执行主算法,DM642A只作数据的调理工作。当确定执行哪种方式的显示时,也就确定了对DM642A所采集的哪些数据加以使用。这个过程由DM642B发出请求,再由专门的控制逻辑来控制DM642A传输,也能实现系统的处理要求。

结 语

数据速度问题是实时高速大数据量视频采集处理系统中要解决的关键问题。本文通过采用针对视频多媒体应用优化了的高速DSP和CPLD,以及专用视频编解码芯片,完成了一个四路双制式高清视频采集处理和多窗口显示系统。经过最后调试和测试,该系统能够满足高速实时性的要求,达到了预期效果,并为下一步的多路视频多图像融合显示系统,提供了很好的技术参考。

评论