基于FPGA的同步测周期高精度数字频率计的设计

摘 要:本文介绍了一种同步测周期计数器的设计,并基于该计数器设计了一个高精度的数字频率计。文中给出了计数器的VHDL编码,并对频率计的FPGA实现进行了仿真验证,给出了测试结果。

关键词:频率计;VHDL;FPGA;周期测量

在现代数字电路设计中,采用FPGA结合硬件描述语言VHDL可以设计出各种复杂的时序和逻辑电路,具有设计灵活、可编程、高性能等优点。本文将介绍一种基于FPGA,采用同步测周期的方法来实现宽频段高精度数字频率计的设计。

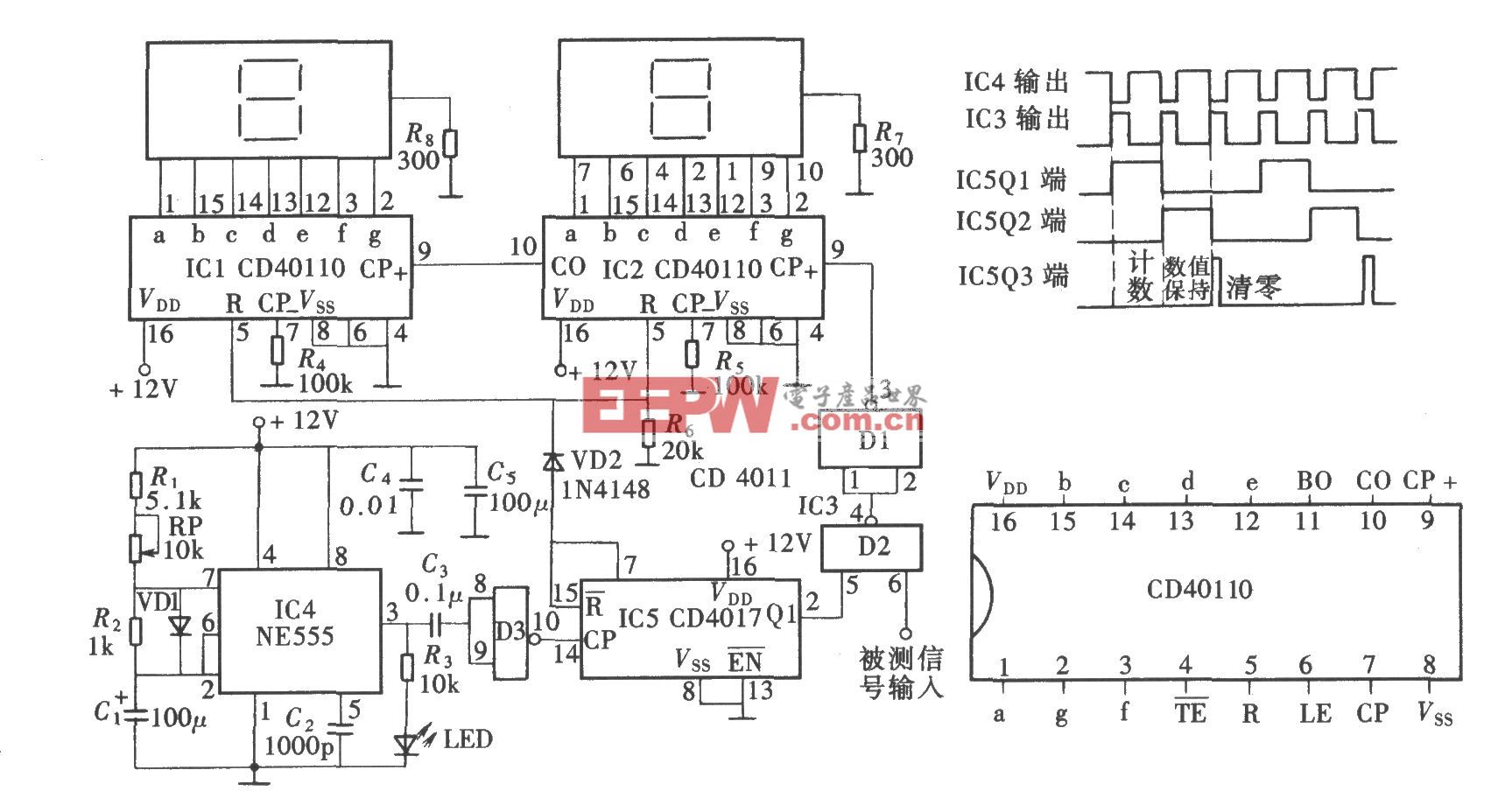

图1 同步测周期计数器

同步测周期频率计的原理

在数字频率计中,测周期计数器是主要的电路,其功能是:使用标准时钟以被测频率信号的一个周期为时限进行脉冲计数。传统的测周期计数器采用门控计数器来实现,即采用一个同被测频率信号周期宽度相同的门控脉冲来控制计数器的计停。其缺点在于无法实现对被测信号的连续测周期计数。

本文设计的同步测周期计数器如图1所示。图中计数器的计数时钟为clk0, 频率为f0;被测信号为clkx,频率为fx。采用一个D触发器对输入的被测信号clkx进行同步,同步输出为s0。在clk0的上升沿到来之前,如果clkx出现了上升跳变,则le信号变为高电平,计数器ct的重载信号和锁存器cout的使能信号有效。当clk0的上升沿到来时,计数器的计数值锁存,同时计数器重载为1,重新开始计数,le变为低电平。计数器在其他时间里进行加1计数,锁存器的值则保持不变。该测周期计数器能在clkx的每个上升沿之后输出计数值,实现了对被测信号进行测周期计数,并始终输出其最新一个周期的计数值,图中cint端输出一个clk0周期宽度的高脉冲,用于指示新的计数值锁存。

图2 同步测周期数字频率计

图3 频率计cint的改进电路

设该计数器的测周期计数值为M0,由于同步测周期法的分辨率为一个标准时钟周期,因此有:

该同步测周期计数器的测周期计数值最小为2,要求被测信号高低电平的宽度大于一个标准时钟周期。

基于上述同步测周期计数器,本文设计了如图2所示的高精度数字频率计。freq_div模块是一个分频器,对标准时钟clk0进行系数为C0的分频。频率计采用了两个同步测周期计数器同时工作,计数值输出端口分别为cout和mout。为了避免由于同步测周期计数器中被测信号和标准时钟不同步,le信号高电平的宽度不固定而造成的计数出错,在实际应用中,采取将被测信号先经过一个D触发器同步后再送入计数器的方法,以保证计数的可靠性,其计数值和频率的关系仍满足(1)式。设cout输出的值为C,mout输出的值为M,根据频率计的结构,对于其中以clkx为计数时钟的计数器,由(1)式得:

同理,对于以clk0为计数时钟的计数器,有:

根据两个测周期计数器的计数值M、C,被测信号的频率按下式计算得到

根据(3)式,计算结果的最大误差为:

相对误差为:

因此,只要使计数值C足够大就可以保证频率测量的精度。将(3)和(4)两式相除并忽略小项得C和C0的关系如下:

给定C0,测周期计数值C的最大可变范围为:。因此,根据实际测量精度的要求,设定适当的分频器分频系数C0,即可保证实际的测周期计数值C的大小在精度要求的范围内。对于上述的数字频率计,如果增大分频器分频系数C0,提高测周期计数器的计数范围,可实现对输入信号宽频段高精度的频率测量。

图4 输入被测信号周期为156ms时的仿真波形

数字频率计的VHDL实现

上述的同步测周期数字频率计在Altera 公司的FPGA开发平台Quartus II中实现,模块采用VHDL语言描述,具有通用性和可重用性。图1中的同步测周期计数器的VHDL描述如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity freq_count is --实体定义

port( reset: in std_logic;

clk0 : in std_logic;

clkx : in std_logic;

cint : out std_logic;

cout : out std_logic_vector(23 downto 0));

end entity freq_count;

architecture ar of freq_count is

signal s0 : std_logic;

signal ct : std_logic_vector(23 downto 0);

begin

p0: process(reset,clk0)

--计数器进程

begin

if reset='0' then

s0<='0';

cint<='1';

cout<=conv_std_logic_vector(0,24);

else

if clk0'event and clk0='1' then

s0<=clkx;

if s0='0' and clkx='1' then

cout<=ct;

cint<='0';

ct<=conv_std_logic_vector(1,24);

else

cint<='1';

ct<=ct+1;

end if;

end if;

end if;

end process p0;

end ar;

测周期计数值M、C分别由mout和cout端口输出,通过一定的接口由微处理器或其他的数据处理模块获取,进行频率的计算和显示,根据实际的应用情况设计输出接口,这里不再详述。当频率计新一轮的测周期计数完成后,计数器通过cint和mint信号指示处理单元来获取数据,其高电平脉冲的宽度为一个计数时钟周期。当计数时钟频率很高时,一些慢速的单片机可能无法捕获,因此(以cint信号为例)增加如图3所示的电路。cint上升沿使D触发器输出引脚cdone置0,通知单片机取数,单片机读结果时,相应的地址信号和读信号有效使图中的cint_set有效,cdone被复位为1,等待下一次cint脉冲的出现。通过该电路,慢速单片机就可以捕获频率计计数完成的指示信号。

为了使频率计的设计更加灵活,频率计中分频器的分频系数也可改为由外部输入。在频率计运行期间,由外部控制器设置不同的分频系数C0,这样可实现更宽范围的频率测量。

频率计的仿真验证

上述数字频率计的VHDL设计在Altera公司的Quartus II开发平台下进行了编译和仿真,图4是在clk0输入10 MHz方波,clkx输入周期为156ms(频率为6.41KHz)方波,分频系数C0取15000时的仿真波形。

本文采用Altera公司的FPGA FLEX10K10LC84-4来实现上述的频率计,计数器计数值的处理和显示由 51单片机来完成,同步测周期数字频率计的参数和测试结果是:计数器宽度为24 bit;分频系数C0取106;计数时钟频率f0为1MHz;FPGA逻辑单元的使用比例为41%;测量的频率范围是1Hz<fx<16MHz;测量误差小于 10-5。

结语

本文设计的同步测周期计数器能够直接对被测信号进行连续的测周期计数,可以在许多频率测量的设计中取代门控计数器,使设计更加灵活。文中采用两个同步测周期计数器设计的数字频率计,无需选择量程便可实现宽频段高精度的频率测量,并在FPGA中实现了系统集成。■

评论