SoC设计:利用SoC互联IP来增强物理布局

Arteris,让人联想起arteries(动脉)。顾名思义,该公司要做SoC中IP和功能块之间互联的动脉。2013年笔者就采访过这家年轻的初创公司,市场副总裁Kurt Shuler的生动讲演就给笔者留下过深刻印象,他提出了NoC(Network on a Chip)概念,这当然不是网络芯片的意思,而是一种在SoC内部加速IP和各功能块之间互联的IP。之所以叫NoC,因为该公司的创始人过去是网络出身,认为可以把网络概念移植到芯片上。

本文引用地址:https://www.eepw.com.cn/article/284667.htm

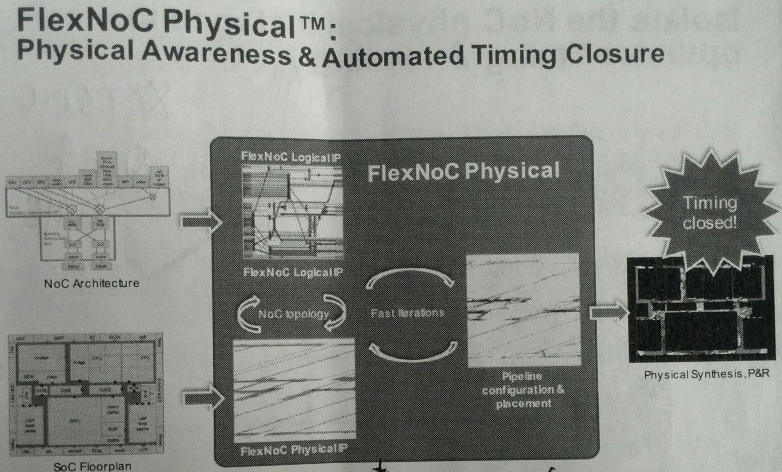

在2015年Globalpress公司举办的Euroasia Press’ tour(欧亚媒体赴美采访团)上,Arteris又带来了哪些新特色?Kurt称在其NoC互联上增加了物理意识(awareness)。

FlexNoC好在哪儿?

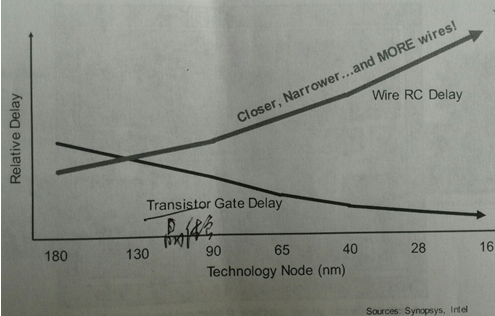

一句话,FlexNoC解决了布局布线的问题。一般地,芯片越小电阻越大,距离更近更容易引起信号干扰,更多的晶体管意味着更多的连线。通过可视化的拓扑俯视图, Arteris IP——FlexNoC自动产生一个架构来优化时序和布线(routing)。

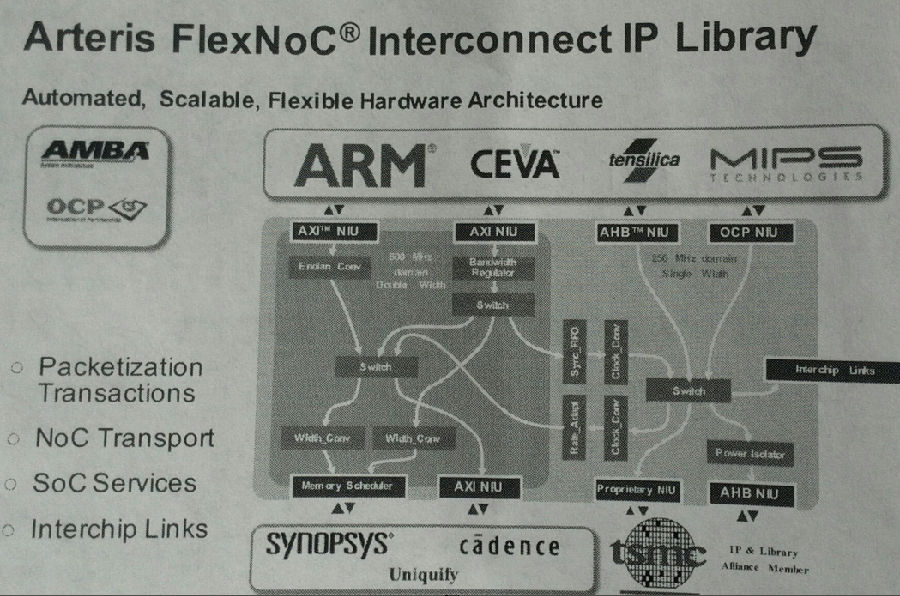

具体地,FlexNoC的互联有三类:FlexNoC工具,FlexNoC库和SoC系统特性。

其中,FlexNoC互联IP库的特点是自动、可扩展、灵活的硬件架构(如下图)。可实现打包交易、NoC传输,提供SoC服务、芯片间连接等。使IP处理器核厂商ARM、CEVA、Tensilica、MIPS,与EDA工具厂商和代工厂商顺利对接。

28nm及以下的物理互联IP挑战是:1.架构需要SoC拓扑的可视化物理影响,2.TL(晶体管逻辑)工程师需要花费数月手工增加管线(pipeline),3.布局工程师得到的互联IP RTL不是物理验证的。

为什么互联如此重要?看看下图的线RC与门延迟之间的鸿沟就可知晓。

SoC IP的布局图大概如下所示。如此复杂,不可能用一个时钟周期走完一个28nm SoC。因为物理距离决定这些管线的数量。例如,NoC在时钟600MHz=1.67ns循环时间时,可用时间是1.42ns;传输延迟0.644ns/mm(最好在28nm、TSMC 28HPM工艺时);管线-管线最大距离是2.2mm。

新的FlexNoC Physical的特点是:具有物理意识与自动时序收敛。1.采用自动化的管线插入,可以节省1~3个月的迭代时间;2.节省10%~15%的互联面积,而不必用过度设计(overdesign)的方法,产生额外的管线数量。3.节省2~4个重要的延迟循环,方法是通过匹配时序目标来实现每个NoC IP,而不是过度设计。4.给布局过程提供的一个更好的起点,来减少布局循环和提高布线的效率。

据悉,TI、三星、Altera和华为海思等是Arteris FlexNoC的客户。

评论