基于FPGA的PCM-FM遥测中频接收机设计与实现

摘要:本文设计实现了一款基于FPGA的PCM-FM遥测中频接收机,在FPGA中实现遥测信号解调、位同步、帧同步等功能,系统码速率、帧长、帧同步码可灵活设置。接收机硬件结构简单,主要包括FPGA、ADC、电源转换芯片、USB接口芯片等常用器件,可单板实现,达到低成本、小型化设计要求。性能测试表明,中频接收机满足设计指标要求,目前该接收机已服务于多个项目。

本文引用地址:https://www.eepw.com.cn/article/274756.htmPCM-FM遥测系统[1]在航空、航天等领域得到广泛应用,国内外遥测厂家均致力于高码率、功能可扩展的遥测产品设计,多功能、通用化、小型化遥测接收系统应用需求越来越迫切,更小、更快、更灵活成为遥测接收技术的又一发展方向。随着数字技术的不断发展,尤其是FPGA技术的发展,遥测中频接收机小型化设计得以实现。本文设计了一款基于FPGA的PCM-FM遥测中频接收机,实现70MHz中频输入PCM-FM遥测信号的下变频、载波跟踪、解调、位同步、帧同步,并最终通过USB接口将数据传给计算机用以数据的存储及分析,接收机码速率、字长、帧长、帧同步码等均可由上位机软件通过USB接口进行设置,所有处理均在FPGA中完成,硬件电路仅由FPGA、AD、电源芯片、晶振等构成,可单板实现,达到小型化设计目的。

1 系统组成与工作原理

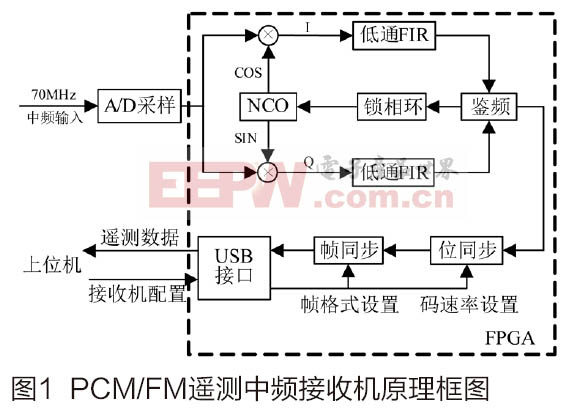

本文设计的PCM/FM遥测中频接收机原理框图如图1所示。

由图1可以看出,PCM/FM遥测中频接收机主要包括A/D采样、数字下变频、鉴频、位同步、帧同步及USB接口等功能模块。70MHz中频输入信号经40MHz带通采样送入FPGA进行处理,在FPGA中产生两路正交信号对A/D采样信号进行数字正交下变频生成基带I、Q信号,I、Q信号分别进行低通滤波后送入鉴频模块,通过叉积鉴频完成解调得到PCM码流,按上位机事先设置的码速率、帧同步码、帧长、时间码等,依次完成PCM码流的位同步、帧同步、时间码合并,最后通过USB接口送入上位机进行遥测数据的存贮和处理。

2 系统详细设计

2.1 数字下变频与FM解调

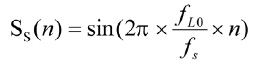

数字下变频与FM解调模块主要包括数控振荡器(NCO)、鉴频器、环路滤波器的设计,数字控制振荡器(NCO)是数字下变频器(DDC)的重要组成部分,它的作用是产生正弦和余弦信号。正、余弦信号如(1)、(2)式所示:

(1)

(1)

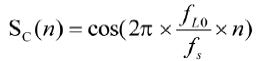

(2)

(2)

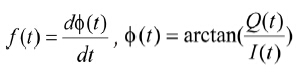

式中,fL0为NCO频率;fs为输入信号的采样频率。由于设计采用带通采样,信号频谱发生搬移。当fs=40MHz时,经过AD采样后,在10MHz、30MHz、70MHz等中心频率上都有所需的有用信号,本设计选择对中心频率为10MHz的有用信号进行混频,此时,fL0为10MHz。在FPGA实现时,采用查表法产生正、余弦信号,建立两个ROM表分别存储0º~90º的正、余弦量化值,通过频率控制字累加值的高两位判断当前的正、余弦值处于哪个象限,对查表输出值进行相应处理,最终得到正、余弦信号[2] 。余弦、正弦信号分别与AD采样输入混频得到I、Q基带信号,经低通FIR滤波器滤波后送入数字鉴频器[3]。假设瞬时频率为f(t),瞬时相位为 ,同相分量为I(t),正交分量为Q(t),由:

,同相分量为I(t),正交分量为Q(t),由:

, (3)

, (3)

得到:

(4)

(4)

对应的数字域表达式为:

(5)

(5)

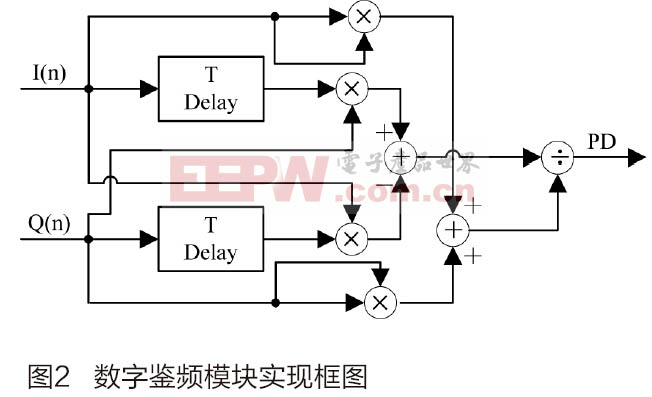

数字鉴频模块的实现框图见图2,鉴频输出即为FM解调得到的PCM码流

fpga相关文章:fpga是什么

晶振相关文章:晶振原理

评论