- CAN协议与其它现场总线协议的区别中有一个是:它使用同步数据传输而不是异步传输(面向字符)。这意味着传输性能得到更有效的发挥,但是另一方面,这需要更加复杂的位同步方法。

- 关键字:

CAN 位时间 位同步

- CAN协议与其它现场总线协议的区别中有一个是:它使用同步数据传输而不是异步传输(面向字符)。这意味着传输性能得到更有效的发挥,但是另一方面,这需要更加复杂的位同步方法。

在面向字符的协议中的位同步实现起来很简单,在接受每个字符的起始位时进行同步。但在同步传输协议中,只有一帧的开始才有一个起始位。这通常不足以使接收器的位采样和发送器保持同步。为了使接收器在帧结束时也能正确采样到接收的位流,就需要接收器不断进行重新同步。重新同步表示在位流中每个有效的信号边沿都可对接收信号的时钟周期进行检测。在信号边

- 关键字:

CAN 位同步

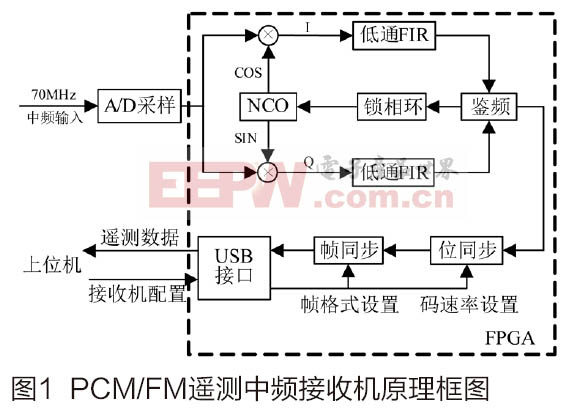

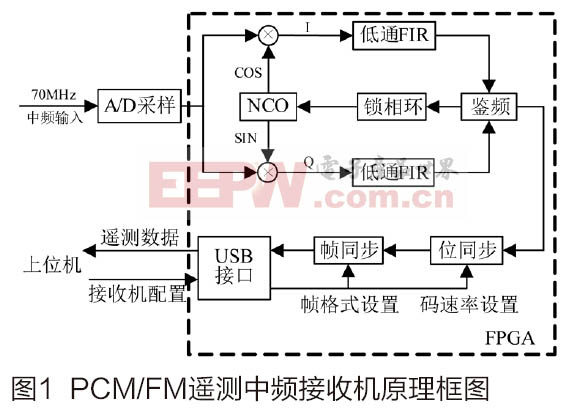

- 本文设计实现了一款基于FPGA的PCM-FM遥测中频接收机,在FPGA中实现遥测信号解调、位同步、帧同步等功能,系统码速率、帧长、帧同步码可灵活设置。接收机硬件结构简单,主要包括FPGA、ADC、电源转换芯片、USB接口芯片等常用器件,可单板实现,达到低成本、小型化设计要求。性能测试表明,中频接收机满足设计指标要求,目前该接收机已服务于多个项目。

- 关键字:

遥测系统 中频接收机 位同步 帧同步 FPGA 201506

- 一般的位同步电路大多采用标准逻辑器件按传统数字系统设计方法构成,具有功耗大,可靠性低的缺点。用FPGA设计电路具有很高的灵活性和可靠性,可以提高集成度和设计速度,增强系统的整体性能。本文给出了一种基于fpga的数字锁相环位同步提取电路。

- 关键字:

FPGA 锁相环 电路设计 位同步

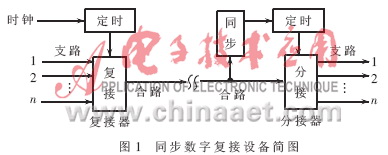

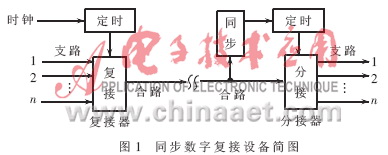

- 摘要: 在简要介绍同步数字复接基本原理的基础上,采用VHDL语言对同步数字复接各组成模块进行了设计,并在ISE集成环境下进行了设计描述、综合、布局布线及时序仿真,取得了正确的设计结果,同时利用中小容量的FPGA实现了同步数字复接功能。

关键词: 同步数字复接/分接 FPGA 位同步 帧同步检测

基群速率数字信号的合成设备和分接设备是电信网络中使用较多的关键设备,在数字程控交换机的用户模块、小灵通基站控制器和集团电话中都需要使用这种同步数字复接设备。近年来,随着需要自建内部通信系统的公司和企

- 关键字:

FPGA 同步数字复接/分接 位同步 帧同步 检测

- 谢 玲, 甘良才, 郭见兵(武汉大学 电子信息学院,湖北 武汉 430079) 摘 要:基于跳频信号的特点,提出了一种隙同步的方法,并采用TMS320C54X系列DSP对隙同步方案进行了硬件仿真和分析。结果表明:该方法实现简单,同步时间短,能够较好 关键词:短波 跳频通信 位同步 TMS320C54X芯片

跳频通信是一种载频按照一定规律变化的多频率移频键控,具有抗干扰性强、保密性好、频带利用率高的特点,易于兼容,便于构成多种通信网。正是由于这些特点,跳频通信系统在现代军事和交通

- 关键字:

TMS320C54X芯片 短波 跳频通信 位同步

- 基于USB2.0的高速无线数传接收设备的数据接收存储方法 北京理工大学电子工程系(100081) 李新昌 摘 要:介绍了一种利用USB2.0接口芯片ISP1581并配合FPGA芯片EP1K30TI144和DSP芯片TMS320F206实现无线数传接收设备中数据接收存储的方法。这种方法具有接口简单、使用方便等特点。 关键词:位同步 帧同步 USB2.0 差错控制

数据接收存储技术是信号采集处理领域内的一个重要课题。利用这种技术,可以把信号的实时采集和精确处理在时间上分为两个阶段,

- 关键字:

USB2.0 差错控制 位同步 帧同步 存储器

位同步介绍

在数字通信系统中,发端按照确定的时间顺序,逐个传输数码脉冲序列中的每个码元。而在接收端必须有准确的抽样判决时刻才能正确判决所发送的码元,因此,接收端必须提供一个确定抽样判决时刻的定时脉冲序列。这个定时脉冲序列的重复频率必须与发送的数码脉冲序列一致,同时在最佳判决时刻(或称为最佳相位时刻)对接收码元进行抽样判决。可以把在接收端产生这样的定时脉冲序列称为码元同步,或称位同步。

实现位同步的方法和载 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473