一种节能型可升级异步FIFO的FPGA实现

现代数字系统中,异步FIFO是一种被广泛应用于跨时钟域进行数据传输的有效方式。异步FIFO主要应用于两种不同时钟域的数据传输,这意味着数据的写入在一个时钟域,而数据的读出却在另一个时钟域,两个时钟完全异步[1]。现代通信系统中,特别是在移动通信系统中,人们对于节能型的产品提出了更高的要求。随着技术的发展,FPGA的技术、性能、稳定性等指标已经得到很大提高,同时FPGA厂商为不同的应用开发提供了各种IP核,大大减少了产品的开发周期,在各大FPGA厂商中,Xilinx的IP核应用比较广泛。但其IP核却没有关于异步FIFO节能方面的设计。在文献[2]中对于FIFO的设计有节能方面的改进,由于其主要应用于ASIC设计,对于FPGA中的应用并不完全适用。

本文引用地址:https://www.eepw.com.cn/article/265945.htm本文提出了一种更加节能而且能应用于高速应用的FPGA设计,同时本文提出一种改进的格雷码二进制码转换结构,在此基础上利用Xilinx的FPGA芯片现有的数字时钟管理模块实现节能方面改进。本文所提出的结构不依赖于现有的IP核,而且可以容易地建立自己的IP核。实际应用中,通过FPGA与DSP进行数据传输可工作于高达100/153.6 MHz读/写时钟域。

1 FIFO的主要结构

1.1 主要的FIFO结构

在所有FIFO结构中,首先要提到的是单时钟域的同步FIFO,虽然同步FIFO在现在的实际应用中很少被使用,但是其结构将有助于理解两个时钟域的异步FIFO的实现。主要有线性结构的FIFO和线性可调结构的FIFO[2]。其结构图如图1。

线性可调FIFO只是在线性FIFO的基础上增加了控制信号以便于容量扩展。从图1中可以看出,无论线性的FIFO还是线性可调结构的FIFO,都是由一些移位寄存器所组成,其主要优点是结构简单容易实现。从数据的输入到输出这一过程看,数据都要经过每个寄存器,当FIFO容量变大时,这类结构的缺点也很突出,如数据从输入到输出的延时时间长,而且能耗比较大。

为了克服以上FIFO结构的缺点,人们提出了很多改善的结构,其中有并行的FIFO、树型FIFO、折叠型的FIFO[2]、环型结构的FIFO[1]。在这些结构中,由于环型的FIFO结构设计相对容易而被广泛采用。本文实现的是基于环型的FIFO结构,并在此基础上进行了节能型的设计改进,使之应用于现代FPGA中。环型结构的FIFO是一种双时钟域的FIFO结构,数据在不同的时钟域中传输时需要考虑数据传输的有效性,同时必需克服数据在不同的时钟中传输时而产生的亚稳态。

1.2 亚稳态

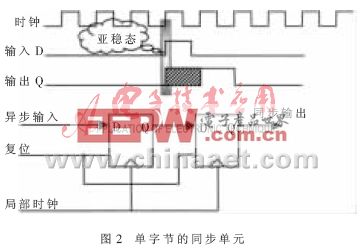

数据在传输的过程中,接收寄存器收到变化的数据时,数据的改变发生在时钟触发沿而导致接受数据出现不稳定的状态[3]称为亚稳态,如图2上部分所示。因此在异步时钟之间进行数据传输常常会用到同步单元。单字节同步单元比较简单,而其常用的同步单元的结构如图2下半部分所示。在多位的跨时钟域数据传输中,情况比单比特的数据传输复杂得多,由于存在多位数据同时变化的情况,为了提高数据传输的稳定性,采用将二进制码转化为格雷码[2]后传输。

2 主体结构与具体实现

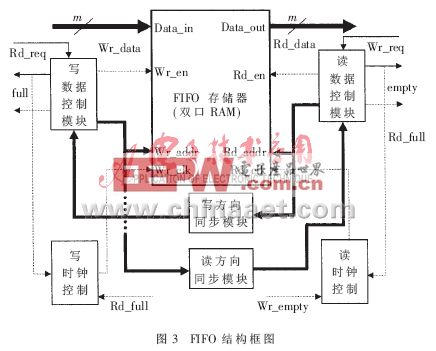

本文所采用的结构是基于环型FIFO结构[1],其整体结构如图3所示。在图3中,总线用粗实线表示,其中总线上的数字(如m)表示总线位宽;控制线用虚线表示,输入、输出的信号(如FIFO空/满信号)用细的实线表示,箭头表示输入/出方向。从图3中可以清楚地看出,整个异步FIFO的结构由读/写控制模块、读/写同步模块、读/写时钟控制模块以及双口的RAM七个模块组成。由于采用模块化的设计结构,以上的结构并不局限于具体的应用,可以很容易设计成实际应用需求的IP核,而且容易升级,相对于传统的设计,增加的时钟控制模块能有效提高能效。

fpga相关文章:fpga是什么

评论