一种节能型可升级异步FIFO的FPGA实现

2.1 FIFO空/满信号的产生

本文引用地址:http://www.eepw.com.cn/article/265945.htm在异步FIFO的设计中,空/满信号的产生是其主要的难点。当写入数据时,写信号指针追上读信号指针的情况,意味着FIFO满的状态。同理在读出数据时,读地址指针追上写地址指针的情况,意味着FIFO为空状态。以上的分析可以得出,不能简单通过读地址指针等于写地址指针来判定FIFO的空/满状态。有效的解决方法在文献[1]、文献[2]中都被采用。若FIFO的深度为N,则其读/写地址指针的宽度应为log2(N)位,读/写地址指针都增加一位,变为log2(N)+1位后,测试读地址指针与写地址指针,当两者相等时,FIFO即为空状态。而当FIFO读地址指针与写地址指针的最高有效位不同而其他有效位完全相同时,即为FIFO满状态,这种循环的地址指针即是环型FIFO的由来。在本文的设计中,空/满信号不仅用于指示FIFO的状态,还用于读/写时钟的控制,从而达到节能的目地。

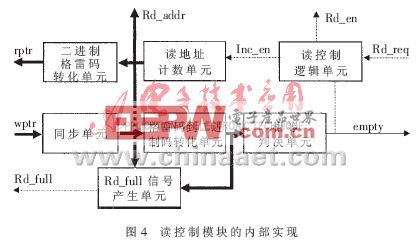

2.2 读控制模块

读数据控制模块主要功能是:根据数据的输出及读请求信号产生用于读数据的控制信号、读地址指针、FIFO空(empty)信号以及用于控制写时钟Wr_full信号(其具体功用在2.3中介绍)。当外部有数据读出请求(Rd_req有效)且FIFO不为空时,使能FIFO的读有效,FIFO输出数据,输出数据完成后读地址指针加1。其中空信号的产生采用2.1中的方法,其内部实现的具体框图如图4所示。

在图4中,读控制逻辑单元主要用于产生读使能信号,依据读请求信号和FIFO的空(empty)信号产生读使能。当有读请求并且FIFO不为空时,读使能有效,同时使地址指针加1。读地址计数器即是一个二进制的计数器,产生输入双口RAM的读地址指针。由于读地址指针要传输到写控制模块,而两模块处于不同的时钟域,为了使数据有效传输到写时钟域,采用先将读地址指针表示的二进制数转化为格雷码(具体实现参见文献[2])后再传输。

2.2.1 同步模块的实现

由于实际应用于系统中时钟频率较高,为了达到稳定,选择了流水线的同步器单元。在图2的基础上增加寄存器的位宽。为了使系统的稳定性增强,采用三级流水线的结构,当然,也可以根据自己实际的需要而增减流水线级数。

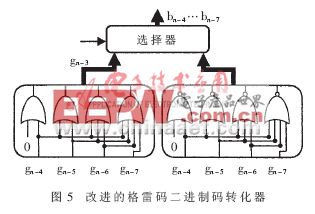

2.2.2 格雷码二进制码转化

为了应用环型指针区别FIFO的空/满信号,需要将传输过来用格雷码表示的写地址指针转化为二进制码,格雷码到二进制码转化的公式如式(1)。设格雷码表示的数据与二进制码有n位,格雷码表示为:gn-1gn-2…g0,相应二进制码表示为:bn-1bn-2…b0。转化公式为:

式(1)中所示的加代表无进位的加法,实现中使用“异或门”即可。但是,完全按照式(1)来实现存在缺点,从式(1)中可以看出,其为一个递推式,最先计算出最高有效位bn-1,最后计算出b0,一次转化完成需要经过n-1个“异或门”的延时,当位数据位增加时,这将成为系统的运行瓶颈。在高速系统中表现的特别突出。提出一种改进的转化单元。将式(1)转化为式(2),如下所示:

可以看出,一次转化只需要一个“异或门”的延时即可完成,但这种结构不适合FPGA中实现。在基本的门电路中,当门电路的扇入数据达到或者超过5时,延时将变得很大,而且大的扇入门电路的实现变得不现实且相当耗资源。将“异或门”的扇入数据限制在4以内(包括4个)。从“异或门”的规律中可以得出,任何变量与逻辑“0”异或,是其本身,而与“1”异或,是其相反变量。将待转化的数据分为四位一组,第一组为(b3…b0),较高的位(如b7…b4)依此细分下去……最高的4位采用如式(2)中进行转化,较低的4位如(bn-4…bn-7)采用如图5的方式转化……这种方式的转化器相对于式(1)实现来说,在不增加门电路资源消耗的基础上,能明显提高转化速度。|

2.2.3 相等判决单元

相等判决单元是一个二进制数比较器,当且仅当读/写地址指针完全相等时,给出空信号有效,否则空信号无效。

2.2.4 Rd_full信号产生单元

Rd_full信号产生单元的结构与FIFO满(full)产生单元的结构相同,Rd_full信号是full信号在读时钟域中的一个复制信号,用于写时钟控制。在时钟控制单元将详细介绍其功能。

2.3 写控制模块

写控制模块的实现与读模块相似,由与读模块相应的单元组成。只是FIFO满(full)时的产生逻辑为当读地址指针与写地址指针最高有效位不同,而其他位均完全相同时,满信号有效。另一不同点体现在Wr_empty信号的产生上,Wr_empty只是FIFO为空(empty)信号时在写时钟域中的一个复制信号,用于读时钟的控制。

2.4 读时钟控制模块

从以上的介绍中可以看出,各个模块的工作统一由时钟来管理,在高速的数字系统中,高速也将带来高的能耗。笔者从实际工作中观察发现,FIFO的工作是需要调配的,只有在DSP需要数据时,才需要FIFO处于工作状态,而在DSP两次需求之间,大量的时间中FIFO是处于空闲状态(这样的情形也符合大多数的实际应用)。可以充分利用这段空闲,让FIFO既能在正常工作时高速而稳定地工作,同时在空闲时能尽可能降低能耗。时钟控制模块即能达到此目的。在空闲时,将FIFO的读/写时钟停止,使空闲的模块处于“休眠”状态。但在正常工作时,时钟能照常管理各个模块。采用Virtex-4芯片内部自带的时钟管理模块(Digital Clock Manager-DCM)[4]来实现。Virtex-4芯片中的DCM提供强大的时钟管理功能,包括:时钟去抖动、频率合成、移相及动态时钟配置。

应用中,主要利用其时钟去抖动和动态时钟配置两项功能。在读时钟控制模块中,当检测到FIFO为空且Wr_empty同时有效时(如同时为高电平),通过DCM即可暂停读时钟。此时FIFO模块中的所有读组件将会停止运行。此时若写入数据,由于Wr_empty处在写时钟域中,写时钟的控制下,Wr_empty将不会有效(变为低电平),此时通过DCM唤醒读时钟,可以正常读出数据,同理可以控制写时钟的暂停与恢复。按照以上的原理设计,用Xilinx ISE 10.1仿真后,得到的仿真波形如图6。clk_in为输入时钟,clk_out为经过控制的时钟,而clk0_out是不经过控制的输出时钟。从图中可以看出,当使能信号为有效(低电平)时,clk_out没有时钟输出,而当使能信号无效时,clk_out时钟正常恢复。可以通过将Wr_empty与empty经过“与非”后接到读时钟clk_en端即可。

2.5 写时钟控制模块

写时钟控制模块与读时钟控制模块原理完全相同,只是输入控制控制信号为Rd_full与full信号。

2.6 双口RAM

双口RAM的实现采用Xilinx的Virtex-4系列FPGA内部现有的资源,通过利用Virtex-4系列芯片中丰富的Block RAM资源,利用原语例化即可生成适合于实际应用需求的双口RAM,参见文献[4]。

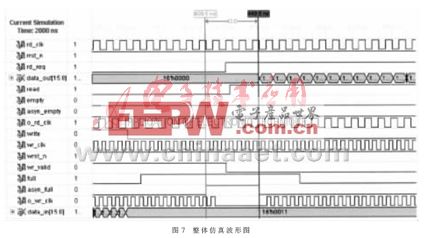

3 整体仿真结果

本方案的实现在Xilinx的ISE10.1上综合,仿真后得到如图7所示整体仿真波形。仿真中,为了便于查看结果,将实际受到控制的读/写模块的时钟引出,分别标记为o_wr_clk,o_rd_clk。由于截图的限制,只能在图中显示FIFO满的情况。空的情况类似。

fpga相关文章:fpga是什么

评论