FPGA研发之道(21)-鸡肋?

通常认为,SOPC是FPGA设计中的鸡肋,“弃之可惜,食之无味”。诚然,SOPC一直不是FPGA的主流应用设计,制约主要因素则是性能,因为作为处理器使用时,处理器主频是其应用范围的瓶颈(SOPC的软核处理器一般运行几十兆到百兆,而一般的嵌入式处理器系统在几百兆到Ghz的主频)。但是若因此说成“鸡肋”,也确实夸张。厂家推出SOPC的设计,其优点主要有一下几点,其一:是差异化竞争的需要。其二,扩大应用范围,争取更多的软件工程师能够从事FPGA设计。其三,可以替代低性能处理器,减少板级的面积和BOM成本。

本文引用地址:https://www.eepw.com.cn/article/265804.htm那么,那么FPGA内部基于软核处理器的系统的主要应用场景有哪些,总结如下:

(1) 管理配置:对于性能无要求的管理配置功能。如某外接芯片或FPGA内部IP在其工作之前,需进行初始化和管理配置,而初始化的模块较多或者管理配置较为复杂,此种情况下,用软件处理更为方便合理。因此,假如FPGA内部资源较为充足,通过内部建立SOPC系统,利用片内的软件给多个外围模块或者内部IP进行初始化的配置管理,即省去配置CPU,减少板级面积,也能便于配置的修改,同时还可以作为前面讲的可测性设计的一部分,用于内部各模块计数统计,功能测试等。

(2) 配合专用硬件加速单元使用: SOPC系统可以通过总线扩展专用协处理单元。即将关键模块硬件化实现,实现高速的处理。举例说,如实现图像处理功能,而SOPC的软件性能不能支持高分辨率图像的处理能力,则可以通过逻辑实现专用的图像处理算法,通过总线接口与SOPC系统连接。,SOPC只作为数据的管理和调度使用。 此外厂商还这么提供了SOPC优化手段,例如通过算法指令分析,确定最多的操作,通过专用指令硬件实现,通过在程序中调用专用指令,也是能够提升性能的方式之一。

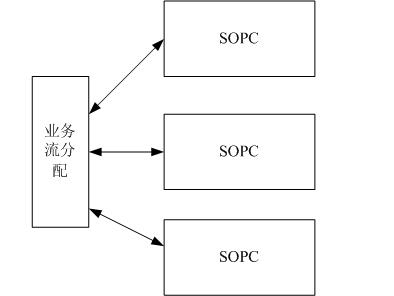

(3) 多核并行:这里多核并行通常意义不同,指通过多个SOPC系统,并行执行,可以提升系统的性能。对于单指令集多数据流的业务,通过将业务流分配到多个SOPC上,通过多个SOPC系统并行处理的方式,来提升整个系统的性能。此种情况下,通过多个SOPC系统并行处理,需满足几个条件:(1)即业务之间没有关联性,不需要再多个SOPC之间进行数据的交互,否则会影响整个系统的性能。(2)程序区不能太大,最好全部存储在片内RAM中。而不用占用外部存储区(DDR或者SRAM),否则,多个片上存储系统争抢外部存储区,可能会造成系统性能的瓶颈,如需存储在片外,则接口竞争部分则是关键设计。

SOPC就像一个偏科生,其优点和缺点都是那么明显,即其强大的灵活性和可编程性,配置其可怜的主频。但是通过一系列提升性能的手段,SOPC在某些业务中也可以大显身手,尤其是需求频繁变更的业务,将变化部分通过软件实现,而不变部分硬件化实现,可以更快的满足市场的需求。

最后,软核CPU处理能力的瓶颈,也促使现有FPGA厂商提供了基于硬核CPU的SOC+FPGA的解决方案,而这些的努力将促进FPGA应用场景的扩展。FPGA广阔天地,大有可为。

评论