一种基于多核处理器DM8168的视频处理方法

摘要:随着1080P高清视频以及4K超高清晰视频的普及和应用,基于传统单核DSP处理器的视频信息处理已有些力不从心。为此TI公司推出了一款专门用于高清视频处理的多核DSP处理器,它拥有4个不同类型的处理器,使得视频处理达到了一个更高水平。本文分析研究了该处理器的多核DSP结构及应用开发方法,并对多核间的协调工作及负载情况进行了测试分析。

本文引用地址:https://www.eepw.com.cn/article/263034.htm引言

以DSP为核心的处理器凭借自身硬件结构的优势和算法优化使得一般的嵌入式产品在视频应用领域得到了广泛的应用。随着高清视频应用的增多,传统单核DSP处理器已经不能很好地满足应用需求了。为此,TI公司推出了一款专门针对高清大数据量快速计算的专用多核DSP处理器DM8168。与传统单核DSP或ARM+DSP的异构多核结构相比,DM8168集成了4个不同类型的处理器,除了传统ARM+DSP结构外,DM8168还拥有两个专门针对高清视频的图像处理器。因此,研究如何基于这种复杂的多核DSP进行应用设计,是有一定实用价值的。

本文在一款基于多核DSP DM8168处理器的SEED-DVS8168平台上,研究了16通道D1数据格式60 fps的大数据量高速视频采集及压缩的实现方法,并且对DM8168实现过程中4个核心处理器的负载进行了测试和分析。

1 硬件平台结构

TMS320DM816是TI公司推出的达芬奇(DaVinci)硬件平台。它在DM8168开发板上拓展了16路模拟输入口,集成了多种外设接口。DM8168硬件平台为TI的高性能异构多核SoC片上系统,该平台集成了一个主频为1.2 GHz的ARM Cortex—A8处理器,一个主频为1GHz的C674x DSP以及3个主频为600 MHz高清视频图像协处理器(High Definition Video/Imaging Coprocessor,HDVICP),以及一个高清视频处理子系统(Hight Defi nition Video Processing Subsystem,HDVPSS)。多核DSP系统应用中,各处理器在硬件上相互独立、相互配合,极大地提升了整个系统的效率。本文针对DM8168集成的4片TVP8158对16路60 fps视频的采集压缩过程进行了研究,并对结果进行了分析。硬件平台结构如图1所示。

1.1 ARM Cortex—A8处理器

ARM Cortex—A8是一款专门针对多任务应用的高性能哈佛结构处理器。本文中ARM Cortex—A8处理器主要用于控制管理各个从处理器,配置和调节各子系统的协同工作,管理外部设备及外部存储器。

1.2 高清视频处理子系统HDVPSS

HDVPSS集成了两个独立的视频捕捉输入端口VIN0、VIN1,每个VIN口又分为A、B两组,即VINOA、VINOB、VIN1A、VIN1B。每个TVP5158复合了4路视频送入VIN口,HDVPSS采集到数据之后利用内部硬件把视频抽离分解出来进行后期处理,捕捉时钟高达165MHz。此外,HDVPSS每个视频输入端口支持缩放、像素格式转换、支持1路高达1080P60或8路复用的D1数据处理。功能上,HDVPSS集成了两个视频处理引擎,具有去隔行处理、降噪、格式转换、视频输入/输出等数据处理能力。

1.3 高清视频协处理器HDVOCP

HDVICP是一个视频编解码硬件加速器,可以最大支持1080P60标准高清视频的编解码流。硬件加速可支持MPEG1/2/4 ASP/SP、H.264 BL/MP/HP、VC-1 SP/MP/AP、RV9/10、AVS-1.0等主流的编解标准。HDVICP集成了运动估计加速引擎、帧内预测估计引擎、熵编/解码器等硬件模块。HDVICP直接在硬件上提升了原本复杂的数字图像处理运算,从而增强了HDVICP的视频处理能力。HDVICP的内部结构如图2所示。

在外部,HDVICP与其他处理器之间通过邮箱中断以及硬件自旋锁来实现。邮箱中断通过写寄存器的方式向某个从处理器发送中断信号,自旋锁机制则为访问系统共享资源提供了完善的解决方案;内部,同步箱负责所有嵌入式模块的调度,同步各加速器之间的参数以及数据。

1.4 数字信号处理DSP

C674x DSP内核是TMS320C6000 DSP平台上的高性能浮点数字信号处理器,其除了具有传统DSP的硬件运算加速器单元外,还具有SPLOO P、压缩的指令集、增强的指令集、异常处理以及优先级管理,完备的硬件支持使得C674x DSP在应用中具有强大地数据信号处理能力。本系统研究中将传统的视频采集及压缩编码这类算法从DSP模块中分离出来,极大地减轻了DSP的负载,使多核DSP协同工作的环境、性能得到了极大的优化。

2 系统软件设计

DM8168的主处理器是ARM Cortex—A8,开始上电之后U-Boot引导其从ROM中启动Linux,一旦启动成功,ARM Cortex—A8便引导从处理器C674x DSP和媒体控制器的电源管理、重启控制以及设置可执行文件的入口到相应寄存器中,完成这个软件运行环境的建立。

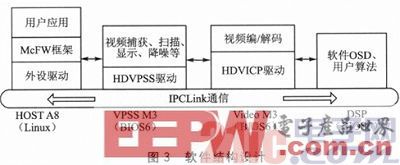

结合DM8168硬件平台的特点,软件系统整体划分为4个模块。其中ARM为主控模块,运行Linux系统,主要负责整个系统的控制以及外设管理;另外3个内核运行BIOS6系统,其中VPSS M3运行在HDVPSS上,主要管理视频的采集、存储以及输入/输出;Video M3运行在HDVICP上,主要负责视频的编解码;C674x DSP主要执行软件的显示策略以及用户算法。软件结构设计如图3所示。

多通道视频处理框架(Multi—channel FrameWork,McFw)中对视频处理常用的捕获、压缩编码、解码、显示等处理过程进行了优化,该框架下的视频处理以Link为基本处理单位进行。视频传递采集、编码以及显示过程大致分为以下几个过程。

(1)原始采集过程

系统获得采集任务之后,首先初始化采集参数,包括采集设备的检测、需采集的视频格式、输出格式等。稍后调用McFW框架下的System _linkCreate()创建CaptureLink,调用System_linkStart()进行视频采集,模拟信号经过主板上集成的4片TV5158解码芯片之后转换为16ChD1 YUV422i 60fps的数字信号传递给VPSS协处理器,等待下一步处理。

评论