如何在集成电路中减少天线效应

如摩尔定律所述,数十年来,集成电路的密度和性能迅猛增长。众所周知,这种高速增长的趋势总有一天会结束,人们只是不知道当这一刻来临时,集成电路 的密度和性能到底能达到何种程度。随着技术的发展,集成电路密度不断增加,而栅氧化层宽度不断减少,超大规模集成电路中常见的多种效应变得原来越重要并难 以控制。天线效应便是其中之一。在过去的二十年中,半导体技术得以迅速发展,催生出更小规格、更高封装密度、更高速电路、更低功耗的产品。本文将讨论天线 效应以及减少天线效应的解决方案。

天线效应或等离子导致栅氧损伤是指:在MOS集成电路生产过程中,一种可潜在影响产品产量和可靠性的效应。

目前,平版印刷工艺采用“等离子刻蚀”法(或“干法刻蚀”)制造集成电路。等离子是一种用于刻蚀的离子化/活性气体。它可进行超级模式控制(更锋利边 缘/更少咬边),并实现多种在传统刻蚀中无法实现的化学反应。但凡事都有两面性,它还带来一些副作用,其中之一就是充电损伤。

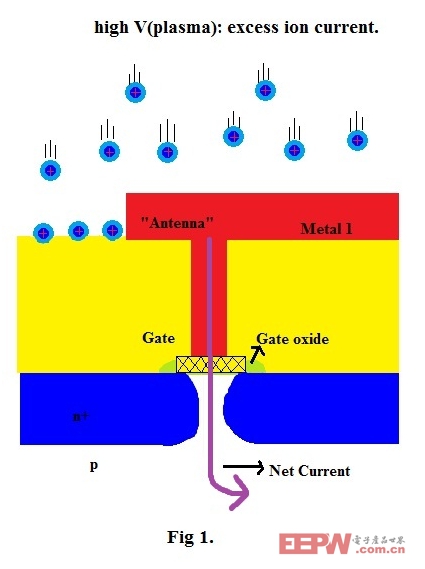

等离子充电损伤是指在等离子处理过程中,MOSFET 中产生的栅氧化层的非预期高场应力。在等离子刻蚀过程中,大量电荷聚集在多晶硅和金属表面。通过电容耦合,在栅氧化层中会形成较大电场,导致产生可损伤氧 化层并改变设备阀值电压(VT)的应力。如下图所示,被聚集的静电荷被传输到栅极中,通过栅氧化层 ,被电流隧道中和。

图1:等离子刻蚀过程中的天线效应。

显而易见,暴露在等离子面前的导体面积非常重要,它决定静电荷聚集率和隧穿电流的大小 。这就是所谓的“天线效应”。栅极下的导体与氧化层的面积比就是天线比率。一般来讲,天线比率可看做是一种电流倍增器,可放大栅氧化层隧穿电流的密度。对 于给定的天线比率来说,等粒子密度越高,隧穿电流越大。更高的隧穿电流意味着更高的损伤。

3种等离子制造过程

导体层模式刻蚀过程——累积电荷量与周长成正比。

灰化过程——累积电荷量与面积呈正比。

接触刻蚀过程——累积电荷量与通过区域的面积成正比。

天线比率(AR)的传统定义是指“天线”导体的面积与所相连的栅氧化层面积的比率。传统理论认为,天线效应降低程度与天线比率成正比(每个金属层的充电效果是相同的)。然而,人们发现天线比率并不取决于天线效应,还需要考虑布局问题。

电路相关文章:电路分析基础

pic相关文章:pic是什么

电荷放大器相关文章:电荷放大器原理

评论