如何在集成电路中减少天线效应

布局对充电损伤的影响

充电损伤的程度是一个几何函数,与极密栅线天线相关。但是由于刻蚀率的差异反映出的刻蚀延迟、等离子灰化和氧化沉积以及等离子诱导损伤(PID)的原因,使得充电损伤更容易受到电子屏蔽效应的影响。

图2:布局对充电损伤的影响。

因此,天线效应的新模式需要考虑刻蚀时间的因素,如公式1。而通过插入二极管或桥(布线)控制天线效应,可以更好地预测天线效应,如公式2所示。

![]()

其中, Q指在刻蚀期间,向栅氧化层注入的总积累电荷。

![]()

A为导电层面积,等离子电流密度J下的电容容量为C

a为栅极面积,等离子电流密度J下的电容容量为a

α为电容比

P为天线电容器的周长

p为栅电容器的周长

ω为等离子电源的角频率

根据基于PID的新模式,PID不取决于AR,但是天线电容与栅极电容的比例是PID的良好指标。PID取决于等离子电源的频率,当氧化层《4nm,PID将对应力电流变得不敏感。在不增加J的情况下,增加栅极的介电常数,可增加PID。

减少天线效应的设计解决方案

下面几种解决方案都可以用来降低天线效应。

1. 跳线法:通过插入跳线,断开存在天线效应的天线并布线到上一层金属层;直到最后的金属层被刻蚀,所有被刻蚀的金属才与栅相连。

2. 虚拟晶体管:添加额外栅会减少电容比;PFET比NFET更敏感;反向天线效应的问题。

3. 添加嵌入式保护二极管:将反向偏置二极管与晶体管中的栅相连接(在电路正常运行期间,二极管不会影响功能)。

4. 布局和布线后,插入二极管:仅将二极管连接到受到天线效应的金属层,一个二极管可保护连接到相同输出端口的所有输入端口。

消除天线效应最重要的两个方法便是跳线法和插入二极管。接下来,我们将详细讨论这两种方法。跳线法是应对天线效应最有效的方法。插入二极管可解决其他天线问题。

跳线法

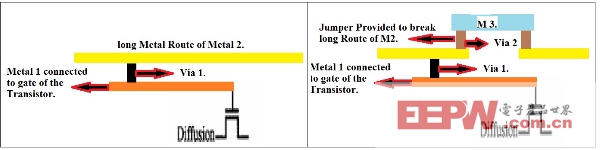

跳线是断开存在天线效应的金属层,通过通孔连接到其它金属层,最后再回到当前层。如下图所示,跳线法将很长的天线分成若干短天线,减小连接到栅输入的电线面积,从而减少聚集电荷。

图3:跳线法减少天线效应示意图。

电路相关文章:电路分析基础

pic相关文章:pic是什么

电荷放大器相关文章:电荷放大器原理

评论