详解TPS5432x/62x, TPS54x18/x19低电压输入下电二次启动问题

摘要

TPS5432x/62x 是德州仪器推出的4.5V~17V 宽电源电压输入范围,输出电流最高可达6A的同步降压SWIFT™系列转换器,TPS54x18/x19 是2.95V~6V 窄电源电压输入范围,输出电流最高可达7A 的同步降压SWIFT系列转换器。该系列器件都具有热性能增强的QFN 小体积封装,专为板级空间要求苛刻的应用优化设计,其内部集成的高边和低边MOSFET 大大增强了其转换效率并具有逐周期限流的过流保护机制。但该系列器件在实际低电压输入应用中可能会出现下电时输出二次启动的现象,本文以TPS54622 器件为例,针对该问题的产生原因进行了研究分析并给出了相应的解决方案,彻底消除了输出电压过冲问题,拓宽了TPS5432x/62x 系列和TPS54x18/x19 系列的应用范围。

TPS54622 是德州仪器推出的4.5V~17V 宽电源电压输入范围,输出电流可达6A 的同步降压SWIFT™系列转换器。该器件具有热性能增强的3mmx3mm QFN 小体积封装,专为板级空间要求苛刻的应用优化设计,其内部集成的高边和低边MOSFET 大大增强了其转换效率并具有“打嗝式”(Hiccup)的过流保护机制。但该器件在实际使用过程中,低电压输入时(例如5V~6V 输入)输出电压在下电过程中会出现多次过冲,最高尖峰幅值在负载为恒阻模式(CR Mode)下可达约1V,有可能影响供电后端微控制器及处理器的正常工作。

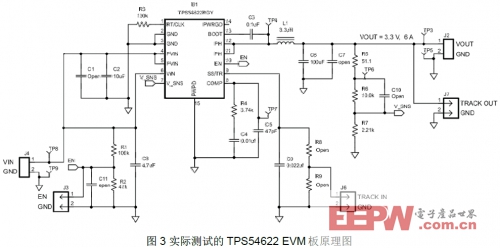

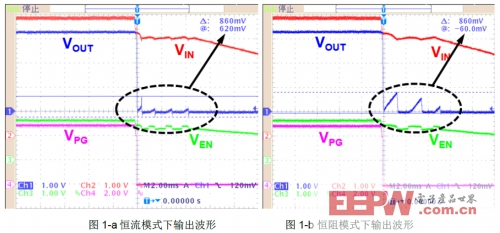

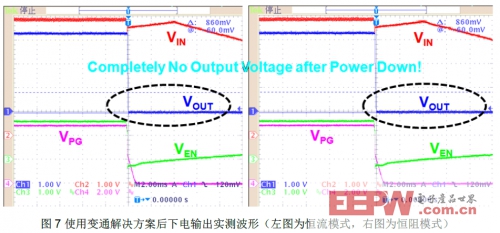

实际实验中测试抓取的TPS54622 输出波形如图1-a,图1-b 所示,整个测试框架示意图如图2所示,测试电路原理图如图3 所示。实际测试中使用TPS54622 的评估板 (TPS54622EVM-012)作为被测对象,测试条件如下:

①输入电压VIN=5.0V

②输出电压VOUT=3.3V

③输出电流IOUT=3A,使用电子负载分别设定为恒流和恒阻模式进行测试

在图1-a 和图1-b 中,VIN 代表输入电压波形,VOUT 代表输出电压波形,VEN 代表使能端波形,VPG代表芯片电源正常(Power Good)引脚波形。从图1-a 和图1-b 中可以看出输入电压下电后,输出电压VOUT 没有立即变为0V,而是经过多次波动后才降为0V。实际测试恒阻模式下过冲尖峰高达0.86V,这种输出尖峰将大大干扰从此电压获取电源的MCU 及处理器的正常工作,使本已下电停机的MCU 或处理器再次启动,影响系统工作的稳定性,这在系统电源轨为0.9V、1.2V 等环境下表现的更为严峻。因此,为达到TPS54622 的电压使用范围(芯片数据手册标称工作范围为4.5V~17V),有必要对此问题进行深入分析并找到变通的解决方法。

2 TPS54622 输出过冲尖峰问题根源分析

从图1a 和图1b 中可以看出,当输入下电,芯片关断之后,由于输入电流在输入引线上产生的压降消失,同时由于线路上寄生电感的作用,导致输入电压会升高,从而导致了的芯片的二次启动。为了解决这个问题,关键是要提高TPS54622 的欠压关断的回差电压。

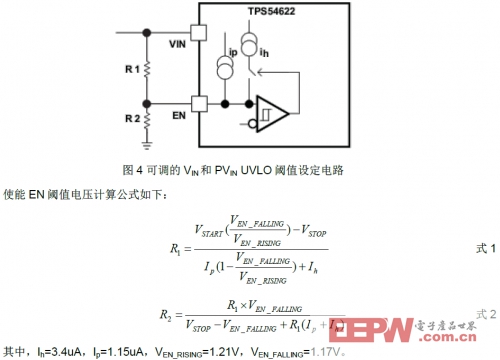

TPS54622 具有EN 使能引脚并具有迟滞功能,使能电压上升阈值典型值为1.21V,下降阈值典型值为1.17V,回差电压为40mV。同时芯片内部使能引脚EN 内部上拉电流源ih 可以用来灵活调节欠压保护的回差电压,通过图4 的两个外接电阻病通过调节电阻的阻值就可以灵活的设定输入欠压保护的迟滞电压。

TPS54622 输入VIN UVLO 阈值电压设置在数据手册中给出了三种配置,考虑到用户的实际使用情况,往往将PVIN 和VIN 短接到一起,本文阈值电压设置如图4 电路所示,计算公式如式1、式2。

可以看出,通过改变电阻R1 和R2 的阻值,可以获得不同的Vstart 和Vstop 的电压,因此也就可以获得期望的回差电压Vstart – Vstop。在本文的测试电路中,设定VIN 约为4V 时,使VEN_RISING约为1.2V,所选取的分压电阻R1=100kΩ, R2=47kΩ。

但是由于TPS54622 VIN 输入电压范围为4.5V~17V,VIN 内部UVLO 上升电压阈值典型值为4V,迟滞回差电压典型值为150mV。当输入电压较低的时候,例如5V 输入,考虑到实际的5V 电压可能会有一定的误差,所以使能引脚EN 的启动电压必须低于5V(如4.5V),但这样留给使能引脚EN 做回差的空间就很小,所以很难通过设定使能引脚EN 的电阻值来获得足够的回差范围。另外从前面VIN UVLO 的介绍中也可以看出芯片自身的UVLO 回差电压也不够大(典型值150mV),这样就不可避免的产生第1 节描述的问题。

3 消除输出过冲的解决方法

前面已经分析了导致输出二次启动产生尖峰的根本原因在于低压输入条件下有限的回差电压空间以及输入VIN UVLO 功能的作用使得使能引脚EN 在芯片下电时没有立即低于门限电压,而是反复波动几次导致了TPS54622 的二次启动,因此,解决此问题的思路就是想办法在芯片下电时强制将使能引脚EN 拉低低于关断门限电压,彻底关闭芯片输出,从而消除二次启动带来的输出尖峰。

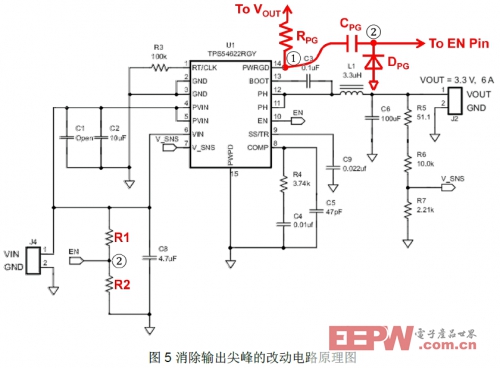

本变通解决方案在原有EVM板电路基础上增加了RPG、CPG 和DPG 三个元件,由于TPS54622 具有电源正常(Power Good, PG)输出指示功能,且当输出电压低于稳压输出的92%或高于稳压输出的106%时,就会驱动PG 引脚使其拉低。本方案的思路是利用电容两端电压不能突变的原理,在PG 引脚和使能EN 引脚之间跨接一无极性电容器,当输出电压跌落低于稳压值的92%时,PG 引脚变低,同时将使能EN 引脚拉低,从而在输入电压反弹的时间段内能够保证使能EN 引脚电压低于开启电压,彻底关闭芯片输出。由于PG 引脚为漏极开路结构,电阻RPG 用于上拉PG 引脚,取值为10kΩ~100kΩ 之间,电容CPG 取值为1uF 即可,取值过大需要较长放电时间,过小无法将使能EN 引脚彻底关闭。

因此,节点②处的电压理论上瞬间将会跳变为-1.436V,实际测试该节点电压约为-0.9V(如图6所示)。该负电压超出了器件手册规定的最大极限值-0.3V 的范围,会造成芯片损坏。为了避免该情况的发生,节点②处的EN 使能引脚需要对地增加一反向肖特基二极管DPG 进行电压钳位保护。

最终本电路在相同测试条件下测试波形如图7 所示。从图7 中可以看出VOUT 在下电之后由于EN引脚被彻底拉低使得芯片完全关闭输出,从而彻底消除了输出尖峰问题。

值得注意的是,由于增加一个电容连接在EN 引脚,上电时有一定的电容充电时间,从而会引起输出电压的延迟,实际测试的延迟时间对比图如图8 所示,从图中可以看出,采用本解决方法后会增加约50ms 的输出延迟时间。

4 结论及总结

本文研究了TPS54622 在低电压输入情况下输入电源下电后输出电压出现二次启动并产生较大尖峰问题,并且该问题实测发现同样存在于TPS5432x/62x 系列和TPS54x18/x19 系列器件中。本文对该问题产生的根源进行了分析并给出了一种消除该尖峰的简便易行解决方法,实际测试该方法彻底消除了下电后输出电压的二次启动过冲尖峰现象。

评论