移动处理器发展新方向,整合更多的GPU将成为主流?

高阶行动装置对多媒体等视觉体验的要求愈来愈高,促使行动处理器开发商大举整合更多GPU核心,期借助平行运算能力,分散CPU运算负担,进而强化绘图与视觉表现。

本文引用地址:https://www.eepw.com.cn/article/241702.htm在全球消费性市场中,智慧手机与平板装置无疑是最热门的产品,根据顾能(Gartner)所发布的最新预测指出,2013年手机出货量将超过十八亿支,较2012年成长3.7%;平板的出货量将上看一亿八千四百万台,成长42.7%,呈现高速增长态势。

尤其值得关注的是高阶行动装置产品更不断推陈出新,给用户的视觉性应用体验已接近个人电脑(PC)、电视等级,即可提供丰富、流畅的二维(2D)或三维(3D)使用者绘图介面(GUI)、视网膜(Retina)级的高画质、快速的网页呈现及摄影功能,以及更逼真的3D游戏等。

在一台小小的行动装置上要达到这些使用体验,对于开发者而言,设计门槛已愈来愈高。以3D游戏为例,要让行动装置达到与PC、电视同级的游戏体验,须提升的视觉效果包括实体表现、动态照明、高动态范围材质(HDR Texture)、先进阴影效果、几何细节、次表面散射(Subsurface Scattering),以及动态反射(Dynamic Reflection)等。

所幸,最关键的行动处理器架构不断升级,除出现整合中央处理器(CPU)和绘图处理器(GPU)的异质多核心架构外,GPU的数量及处理能力也大幅提升,成为实现流畅、长时效视觉体验的最大功臣。以下将剖析先进GPU在架构上的变化与最新进展。

实现更酷炫绘图功能 异质多核心SoC势不可当

愈来愈多中高阶行动装置配置四核心CPU的行动处理器,以辉达(NVIDIA)的Tegra系列来说,自Tegra 3开始,就已进入4+1的多核心架构,即四颗效能核心加一颗省电核心,而最新一代的Tegra 4,同样采用4+1的多核心架构,但处理器核心从前代的Cortex-A9提升为Cortex-A15;至于Tegra 4i则仍采用Cortex-A9(r4)CPU。

虽然CPU的数目愈多,意味着处理效能也跟着提升,但因CPU的序列处理特性,愈多核心意味着应用程式撰写亦愈困难;相较之下,由于GPU具备平行处理特性,能以近线性化来扩充效能,因此增加GPU数目所提升的效益,会比CPU显著许多。

在此情况下,整合CPU与GPU的异质多核心架构,就成了必然之势。而当GPU核心更多,也让开发者有更大空间和弹性去做出更酷的绘图效果、更细腻的细节表现及更生动的情境塑造,让行动视觉与游戏的体验大幅提升。

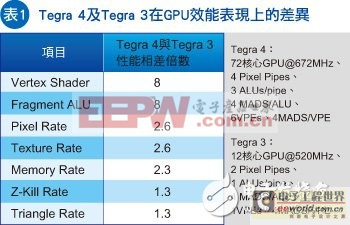

Tegra 4的GPU子系统就是很好的例子,它从前代的十二颗GeForce GPU核心,一举提高到七十二颗,六倍的核心数也带来六倍于Tegra 3的绘图效能。Tegra 4及Tegra 3在GPU效能表现上的差异,请参考表1。在系统配置上,其架构中有所谓的顶点着色器(Vertex Shader)和画素着色器(Pixel Shader);前者让工程师可自订场景(Scene)中顶点的转换过程,后者则是用来控制画面上每个画素的着色计算。

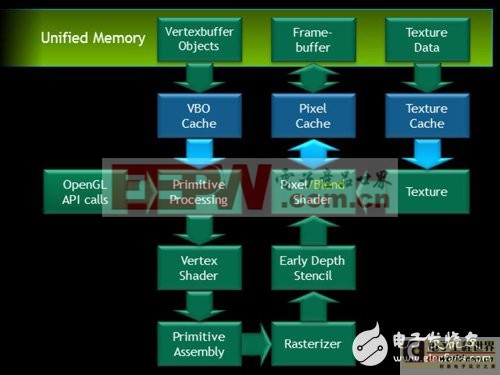

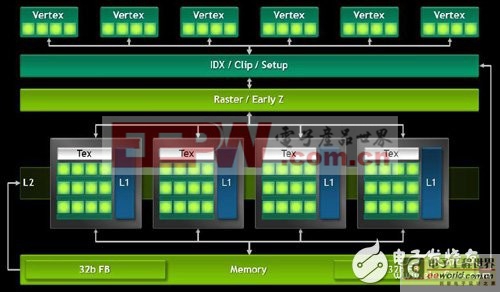

更进一步来看,Tegra 4的作法是将七十二颗GeForce核心拆分为二十四颗Vertex Shader与四十八颗Pixel Shader。其中每四颗Vertex Shader组成一组顶点处理引擎(Vertex Processing Engine, VPE),所以有六颗VPE,分别具有16KB、96-entry快取记忆体,能够有效降低向外部晶片存取资料的需求。在相同时脉下,新的GeForce核心可以带来1.5倍于Tegra 3的效能,而前后代Vertex Shader数量相差六倍,相乘之下差距达九倍之多。 此外,Tegar 4总共具有四组画素管线(Pixel Fragment Shader Pipeline),每组画素管线可细分为三组算术逻辑单元(ALU),每个ALU则是由四颗GeForce核心(即Pixel Shader)组成。在实际运作时,会以ALU做为最小层级的单元,并称为多功能处理单元(Multi-Function Unit, MFU),因此Tegar 4总共具有十二组MFU,MFU可执行函数、三角函数、对数、倒数、平方根及MOV等指令(组合语言中的复制)(图1、2)。

图1 Tegra4的逻辑性绘图处理管线流程图

图2 Tegra 4的GPU架构方块图 降低多核心SoC耗电量 架构设计担当重任

对于行动装置而言,电池的使用寿命与效能/功能表现占有同样重要的地位。同样是四核心行动晶片,因个别架构不同,往往也有不同的效能与功耗表现。以Tegra 4来说,除采用安谋国际(ARM)最先进的CPU核心外,透过可变对称式多重处理(vSMP)架构,可依照使用需求进行调配,让四颗效能核心发挥最大处理能力,并可视工作量,分别自动启用及停用各颗核心,以大幅节省电力。

为了提升续航力,Tegra 4延续Tegra 3的省电概念,在晶片中加入第五颗处理器核心,不过名称从协同核心(Companion Core)改为省电核心(Battery Saver Core)。当装置处于背景处理邮件、社交软体同步,或是播放影片、音乐等低效能需求情境时,系统将关闭效能核心,并使用省电核心负责执行程式。

就晶片设计观之,多核心处理器必定会面临记忆体频宽和整体系统功率的重大瓶颈,为了因应此议题,Tegra 4提出双通道(2x32位元)的记忆体子系统作法。此外,为减少对晶片外记忆体的存取使用需求,Tegra 4的GPU架构中规画顶点、画素、材质(Texture)专用的快取记忆体,让运算任务尽量在晶片内部完成,以提升处理效益和降低功耗。

另一个降低系统单晶片(SoC)功耗的重要策略,就是采用先进的电源管理技术。以Tegra 4来说,即采用多层级时脉闸控(Multiple Levels of Clock Gating)、显示要求群组(Display Request Groupig)、动态电压与频率调节(DVFS)等多种电源管理技术,针对不同使用情境将电源需求降至最低。

运算型摄影架构助力 行动装置影像效能升级

再从应用端来看GPU架构的发展,今日的使用者非常仰赖行动装置来进行照相和和录影功能,且希望达到专业级的效果。不过,相较于相机,手机或平板装置在先天性上就难以配置太大的镜头,这时想得到高品质的影像,就得靠更先进的影像处理技术,甚至是运用电脑演算法来创造影像。

评论