基于FPGA的以太网MII接口扩展设计与实现

引言

传统以PC为中心的互联网应用现已开始转向以嵌入式设备为中心。据网络专家预测,将来在互联网上传输的信息中,有70%来自小型嵌入式系统,因此,对嵌入式系统接入因特网的研究是有必要的。目前有两种方法可以实现单片机系统接入因特网:一种方法是利用NIC (网络控制/网卡)实现网络接口,由单片机来提供所需的网络协议;另外一种方法是利用具有网络协议栈结构的芯片和PHY(物理层的接收器)来实现网络接口,主控制器只负责往协议栈结构芯片的某个寄存器里放上适当的数据。与此同时,用FPGA实现单片机系统接入因特网的方法也日益受到人们的重视。本文提出采用FPGA实现网络协议栈,介绍100M以太网MII接口协议的硬件实现方法,其中的奇偶模块分频器和异步FIFO等通用器件在日常中也很有应用价值。

以太网MII接口协议

IEEE802协议标准系列中,数据链路层包括LLC (逻辑链路控制)子层和MAC (媒体访问控制)子层。其中MAC单独作为一个子层,完成数据帧的封装、解封、发送和接收功能。物理层PHY的结构随着传输速率的不同而有一定差异,在100M和1000M以太网中,依次为PCS子层、PMA子层和PMD子层。MII接口是连接数据链路层和物理层的接口,因为本设计中以太网速率采用100Mb/s,所以MII接口实际连接的是MAC子层和PCS子层。根据协议,要求MII接口具有的功能有:数据和帧分隔符的读写时钟同步,提供独立的读写数据通道,为MAC层和PCS层提供相应的管理信号,以及支持全双工模式。

扩展MII接口功能及其

FPGA实现

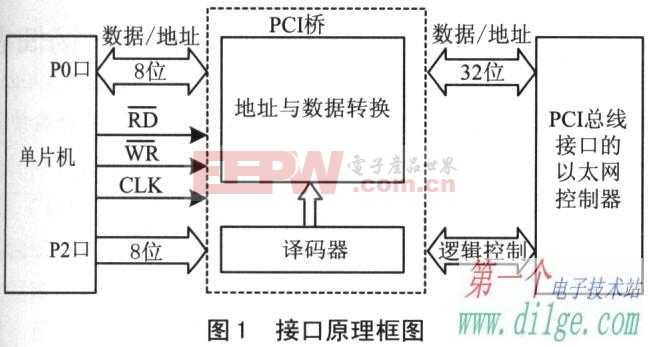

由于100M以太网的物理层采用4b/5b编码,为了扩展MII接口的功能,要求其能够实现直接物理层5位数据和MAC层8位数据的发送接收传输转换。即把从MAC子层用于发送的数据和从PHY用于接收的数据存入数据缓冲FIFO,同时要求MII接口将从PHY传来的信号COL、CRS转为信号Carrier和Collision,并提供给MAC子层用于载波监听和冲突检测,以及发送和接收时的时钟、使能、错误位信号的传送。扩展功能后的MII接口硬件结构框图如图1所示,由4b/5b编解码器、控制信号与4位/8位转换、分频器及双口FIFO 4个模块组成,而且能够同时支持半双工和全双工模式。

在设计过程中,为了考虑测试和支持多种速率传输的需要,要求设计带有分频参数的可实现奇偶分频的分频器和支持能够同时进行读写操作和异步读写时钟的FIFO。这是MII接口设计中的难点,本身也具有很高的实用价值。

分频器相关文章:分频器原理

评论