基于Verilog HDL语言的CAN总线控制器设计及验证

CAN_Core为CAN协议控制器的核心部分,完成CAN协议中的数据链路层的全部功能以及物理层的部分功能,包括LLC子层的接收滤波、超载通知和恢复管理、MAC子层的数据封装/拆装、帧编码、媒体访问管理、错误检测、错误标定、应答和串行化/解串行化、以及物理层的位编码/解码、位定时和同步。CAN_Registers为一寄存器组,外部微处理器可以通过地址直接访问这些寄存器。根据功能框图,设计了CAN总线控制器的程序结构,如图3所示。

1.3 CAN总线各个功能模块的设计

1.3.1 CAN_IML设计

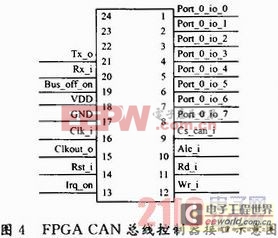

参照SJA1000,设计FPGA CAN总线控制器的接口,如图4所示。

图中Port_0_io_7到Port_0_io_0为地址/数据复合总线。Cs_can_i为片选输入信号。当Cs_can_i为0时允许访问CAN总线控制器。Ale_i为1时,允许对寄存器进行赋值。Rd_i和Wr_i为微处理器的读使能信号和写使能信号。Irq_on为中断输出信号,用于中断微处理器。Rst_i为复位输入,用于复位CAN接口。Clkout_o为FPGA CAN控制器提供给微处理器的时钟输出信号,时钟分频寄存器可禁止该引脚输出。Bus_off_on控制总线关闭和总线开放接口,Tx_o和Rx_i与收发器相连,向总线发送和接收数据。

1.3.2 CAN_Registers设计

设计的CAN总线控制器的寄存器模块包括以下寄存器:模式寄存器、命令寄存器、状态寄存器、中断寄存器、中断使能寄存器、总线定时寄存器0~1、仲裁丢失捕获寄存器、错误代码捕获寄存器、错误报警限制寄存器、接收错误计数器、发送错误计数器、验收代码寄存器0~3、验收屏蔽寄存器0~3、接收信息计数器和接收/发送缓冲器。

1.3.3 CAN_Core设计

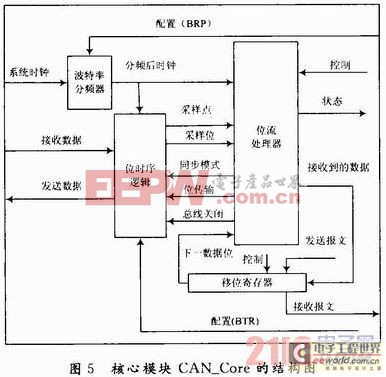

CAN_Core为整个CAN控制器的核心,负责处理CAN的协议。核心模块由4个部分组成,结构如图5所示。

下面简单介绍CAN_Core模块中的位流处理器、位时序逻辑。

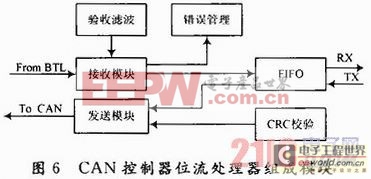

位流处理器是CAN总线控制器中控制数据流的发生器。它还执行总线上的错误检测、仲裁、填充和错误处理等功能。主要有接收模块、发送模块、错误管理模块、CRC校验、验收滤波、FIFO等6个模块组成,如图6所示。其中CRC校验、FIFO、验收滤波在所执行的项目中已经有他人设计完成。

位时序逻辑的设计包括位定时设计、采样点设计、位同步设计3部分。下面以定位时为例介绍其设计。

位定时设计 在位定时设计中采用了一个有3个状态的状态机。3个状态分别对应的是同步段和相位缓冲段1以及相位缓冲段2。传播段占用的时间短,在控制上没有特别的意义,仅作为物理层的传播延时,所以没有设计进状态机,位定时部分的状态机设计如图7所示。

评论