基于1-Wire总线的DS28E01加密芯片原理研究及其在FPGA加密系统中的应用

本文引用地址:https://www.eepw.com.cn/article/233871.htm

FPGA的应用越来越广泛,但也出现了一个问题,那就是FPGA设计的产权保护问题。因为FPGA的工作原理是在系统上电时将片外PROM中的BIT数据流加载到片内的SRAM中,完成对FPGA的编程,从而实现设计者的不同功能,即所谓的可重构技术。这就使得监测FPGA加载管脚的数据流就可实现对FPGA功能设计的复制。因此非常有必要采用加密的技术来保护设计者的知识产权。美国Dallas公司生产的DS28E01就是这样的一款采用1-Wire总线的加密产品。

1 DS28E01芯片介绍

DS28E01采用1-Wire总线串行传送数据,只需要一根数据线和一根地线,最大限度地节省了对被加密器件I/O管脚的占用。DS28E01将1024位EEPROM与符合ISO/IEC110118-3 SHA-1算法的质询响应安全认证结合在一起。该器件能够处理64位或320位长密钥、40位长随机质询码和器件其它数据的SHA-1计算,以提供它和被加密器件之间更高级的安全认证。1024位的EEPROM分为4页,每页256位,带64位暂存器以执行写操作。

SHA-1算法是HASH函数算法中的一种,是一种单向密码体制。它通过直接构造复杂的非线性关系达到从明文到密文的不可逆映射。具有“防碰撞”以及良好的“雪崩效应”,防止了盗窃者利用相似的输入来达到破解密码的可能性。

DS28E01包括6个主要数据部件:1)64位光刻码, 2)64位暂存器,3)四个EEPROM页,每页256位,4)寄存器页,5)64位密钥存储器,6)512位SHA(安全散列算法)引擎。

1-Wire 协议的层次结构中,主机必须首先发送以下七条ROM操作命令中的一条:1) Read ROM,2) Match ROM,3) Search ROM,4) Skip ROM,5) Resume ommunication,6) Overdrive-Skip ROM,7) Overdrive-Match ROM。当以标准速度执行完Overdrive ROM 命令后,器件进入高速模式,所有后续通信均以高速模式进行。成功执行完ROM操作命令后,就可以进行存储器和SHA-1操作,主机可发出9条有效功能命令中的任一条。

2 DS28E01基于1-Wire总线进行FPGA加密的工作原理

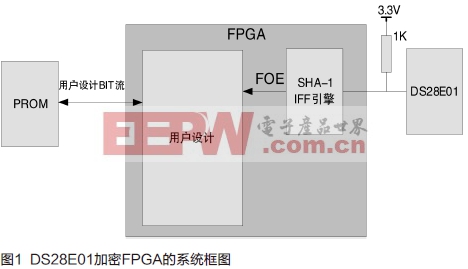

图1是利用DS28E01加密用户FPGA设计的系统框图。DS28E01通过1-Wire总线和FPGA相连,FPGA内嵌一个SHA-1引擎和DS28E01握手。引擎中携带有和DS28E01相同的密钥,这是由用户预先配置好的。1-Wire总线上必须外接一个不大于2.2kΩ的上拉电阻。

具体的加密工作原理如下:

1.上电后,PROM中的用户设计被下载到FPGA中。此时FOE=1,用户设计处于关闭状态。

2.FPGA中的SHA-1引擎产生一个随机数,通过1-Wire总线发送给DS28E01。

3.FPGA中的SHA-1引擎通过1-Wire总线读取DS28E01的器件序列号。

4.DS28E01利用仅仅对用户开放的密钥、器件序列号、随机数、附加常数等通过SHA-1算法来产生一个160位的MAC值。同时FPGA中的SHA-1引擎此时也利用相同的信息通过SHA-1计算来得到相同的160位MAC值。

5.FPGA中的SHA-1引擎通过1-Wire总线读取DS28E01计算出来的160位MAC值。

6.在FPGA的SHA-1引擎中比较两个160位的MAC值,如果相同则FOE=0,用户设计功能被打开。

按照这样的过程即只有SHA-1引擎中的密钥和DS28E01中的密钥完全相同时,用户设计才会开放,这样就可完成对用户设计的IP产权保护。

3 通过1-Wire总线访问DS28E01的协议分析

3.1 通过1-Wire访问DS28E01的协议如下:

1.初始化命令;

2.ROM功能命令;

3.存储器/SHA-1命令;

4.根据命令数据的输入输出。

要通过1-Wire总线访问DS28E01,总线上的数据必须满足协议要求,并符合1-Wire的时序。Wire总线上所有的传输操作均从初始化过程开始。初始化过程由主机发出的复位脉冲和从机发出的在线应答脉冲组成。在线应答脉冲通知主机DS28E01挂接在总线上,并且已经准备就绪。

一旦主机检测到在线应答脉冲,就可以发出DS28E01支持的七条ROM 功能命令中的一条:1) Read ROM,2) Match ROM,3) Search ROM,4) Skip ROM,5) Resume Communication,6) Overdrive-Skip ROM,7) Overdrive-Match ROM。

成功执行完ROM操作命令后,就可以进行存储器和SHA-1操作,FPGA中的SHA-1引擎可发出9条有效功能命令中的任一条:1)Write Scratchpad,2) Read ScratchPad,3) Load first Secret,4)Compute Next Secret,5)Copy ScratchPad,6) Read AuthPage,7)Anonymous Read Auth.Page, 8) Read Memory ,9)Refresh ScratchPad。

3.2 1-Wire 信令

为了保证数据的完整性,DS28E01具有严格的信号协议。该协议在一条线上定义了四种类型的信号:包括复位脉冲和在线应答脉冲的复位序列、写0、写1 和读数据。除在线应答脉冲以外,所有其它信号下降沿均由总线主机发出。DS28E01 能够以两种不同速率通信:标准速率和高速模式。如果没有明确设定为高速模式,DS28E01就以标准速率通信。高速模式下,所有波形均采用快速定时。启动与DS28E01的任何通信都需要初始化过程。

3.3 1-Wire总线上的DS28E01加密指令说明

DS28E01提供7条ROM指令和9条MEM指令,在FPGA加密系统中一般只用到几条就够了。

根据FPGA加密原理所述,FPGA中SHA-1引擎所使用的密钥是由设计者预先配置好的,DS28E01中的密钥也是由设计者在出厂前通过烧写器写好的。为了完成加密过程,FPGA中的SHA-1引擎只需要对DS28E01进行3个操作过程即可:1)写随机数,2)读DS28E01器件ID,3)读DS28E01 SHA-1运算结果,即160位的MAC值。

3.3.1 写随机数

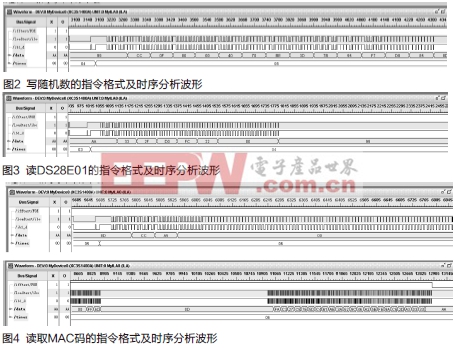

指令格式和时序分析波形如图2 所示,FPGA先发送ROM命令码Skip ROM(CCH),接着发送MEM命令码Write Scratchpad(0F)以及目标地址。

RST为FPGA产生的1-Wire复位脉冲,PD为DS28E01产生的在线应答脉冲,Select是ROM功能命令,WSP为MEM功能命令,TA是目标地址TA1和TA2,之后为要写入的64位随机数,之后是从Select命令到随机数所有字节的8位的CRC16校验值的反码,其后是无效的数据FF。每个字段的数据都是低位在前传输。以下所有命令格式都类似。

1-Wire总线上数据如图中ibo所示,data为将1-Wire总线数据根据协议正序并转成为并行数据,Select=CCh、WSP=0Fh,TA=8000h,64位随机数为40h、70h、BEh、3Dh、78h、95h、F7h、D8h,8位CRC16校验的反码为85h。

3.3.2 读DS28E01器件ID

指令格式和时序分析波形如图3 所示,FPGA发送ROM命令码Read ROM(33H),此条命令允许主机读取DS28E01的八位家族码,48位唯一序列号和8位CRC校验码。

1-Wire总线上数据根据协议被正序并行化后在图3波形中显示为:Select=33h、8位家族码为2Fh、48位唯一的器件ID=00000022FCD0h,8位CRC16校验的反码=99。

3.3.3 读160位MAC码

指令格式和时序分析波形如图4 所示。 FPGA先发送ROM命令码Skip ROM(CCH),接着发送MEM命令码Write Scratchpad(A5)以及目标地址,之后,FPGA将接收DS28E01中从目标地址开始到数据页末尾存储器页中数据,一个FFh 字节和CRC反码。 CRC校验码接收完毕后,FPGA等待一段时间。此时, DS28E01中的SHA 引擎利用相同的密钥、随机数、附加数据及器件识别号来计算160位的MAC。等待SHA-1运算周期结束后,就可读到160位MAC,随后是CRC反码。如果在CRC 校验码后主机继续读取数据,将会到读到无效数据AAh。

从图4中我们可以看到,当读到AAh时,FOE=0,这表明加密芯片计算的MAC值与FPGA中SHA-1引擎计算的MAC值一致。用户设计将开始工作,至此加密过程全部结束。

5 FPGA验证和结论

本加密系统在Xilinx公司 Spartan-6的XA6SLX45-3上进行了FPGA验证。FPGA中的SHA-1引擎采用了Xilinx公司提供的免费IP。采用Verilog语言完成了1-Wire总线的相关分析功能的设计。调试中使用了Xilinx公司的硬件Debug软件ChipScope,抓出了1-Wire总线的相关波形,完成了时序分析。最后该加密系统成功应用于西安某知名IC设计公司的一款FPGA推广产品中。可以看出,在IC设计竞争日益强烈的今天,利用FPGA加密系统来保护知识产权,为公司产品抢占市场先机是IC设计的必由之路。

参考文献:

[1]DS28E01-100 带SHA-1引擎保护的1K位1-Wire EEPROM[R/OL].www.maxim-ic.com.cn

[2]张斌,徐名扬.SHA-1算法及其在FPGA加密认证系统中的应用.中国集成电路,2011(6)

[3]杨春林,张春雷,高山,等.基于DS28E01的FPGA加密认证系统的设计.微计算机信息,2009(23)

[4]刘军志,黄进.基于DS2432和FPGA的IFF加密方法.微计算机信息[J],2007(7):201-202

[5]伍家满,虞礼贞,刘小燕,等.基于1-Wire接口的总线技术即其应用,南昌大学学报,2005,27(1)

fpga相关文章:fpga是什么

脉冲点火器相关文章:脉冲点火器原理 上拉电阻相关文章:上拉电阻原理

评论