控制之道-外部机制为CMOS LDO器件提供限流保护

功率半导体开发越来越趋向在器件支持的功能集中增添新的功能,从而提升电路设计灵活性。低压降(LDO)稳压器的功能可增加的关键领域就是支持外部控制限流。这使其功耗能在无须使用复杂控制的条件下保持在极低等级。

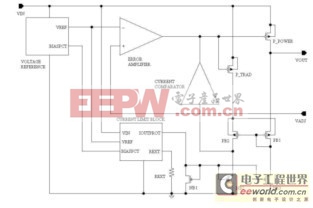

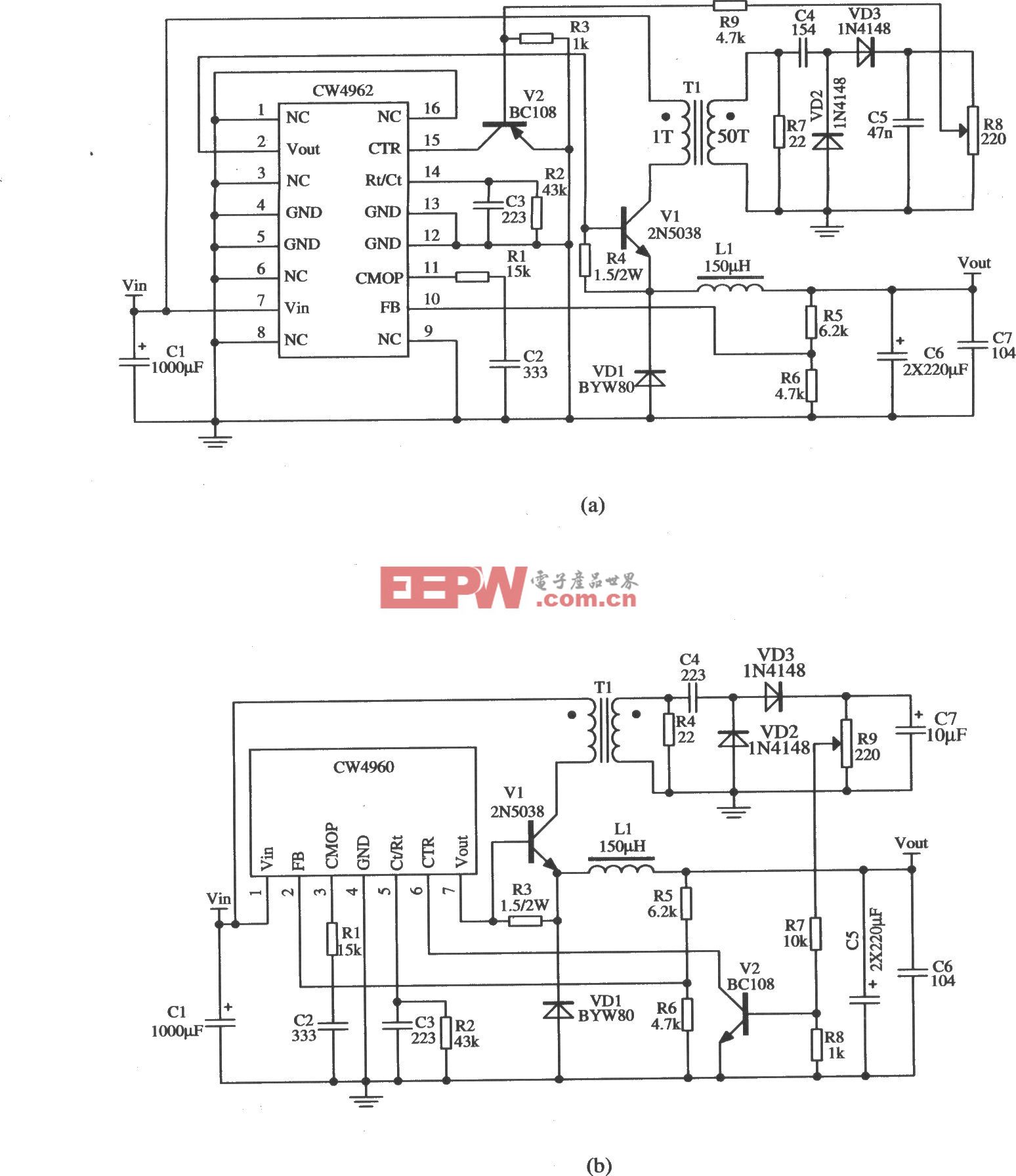

图1显示了可调节软启动CMOS LDO的框图,其中包括采用外部控制的限流保护电路。流过功率晶体管P_POWER的电流通过P_TRAD来复制为低得多的电平,并与NMOS晶体管(NB2)汲取的参考电流比较。一组晶体管(PB1、PB2及NB3)用于将P_TRAD的漏极至源极电压保持为与P_POWER的相同。

如果流过P_TRAD的电流大小达到与工作区域内NB2汲取的电流相同,电流比较器就会控制P_POWER的门极至源极电压,方式是维持已有输出电流的电平(即限流)。通过使用额外的限流模块,就可以使用外部电阻REXT来控制流过NB1(及NB2和NB3)的参考电流的大小。为了恰当控制,REXT的电压应当相对于其电流保持恒定。

图1:包括限流保护功能的CMOS LDO框图。

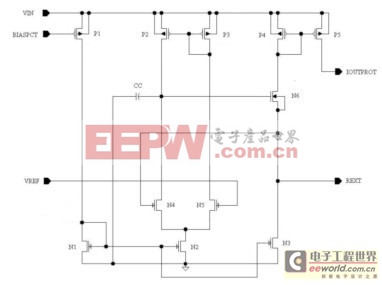

图2:限流模块简化电路图

图2展示的是限流模块的简化电路图。此限流模块实际上作为电压缓冲器工作,为REXT提供参考电压VEXT。所得到的电流IOUTPROT用于偏置图1中连接二极管的NB1。配置为电压缓冲器的运算放大器有两级。第一级是传导级,带有组成有源负载的NMOS输入晶体管(N4和N5)及PMOS晶体管(P2和P3)。第二级是围绕隔离NMOS晶体管(N6)构建的共漏极级。缓冲器的偏置电路由晶体管N1、N2和N3构成,且缓冲器由电压参考模块提供的电流来偏置,几乎提供零温度系数。由PMOST晶体管(P4和P5)构成的电流镜用于从此模块获得输出电流。频率补偿由电容CC在阻抗最高的节点上完成。所有电流镜都针对恰当的过驱动电压而设计,而N6足够大,可以轻易地处理达数十μA的电流。流过N1、N2及N3的电流电平接近1 µA。N3的存在确保存在非零电流IOUTPROT,即使外部电阻完全不存在。N6必须是隔离型NMOS器件,从而维持低门极至源极电压,同时源极电压接近于VREF (即1.25 V)。

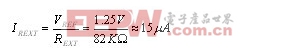

设定流过电阻REXT的电流以确保阻抗值等于或低于100 kΩ,用于目标应用(要求0.3 A连续负载电流或最少0.45 A电流极限)。例如,假定REXT = 82 kΩ及VREF = 1.25 V,即得:

(1)

(1)

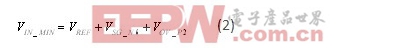

不过,在其它应用中,可以轻易地增加REXT至更大的值。P4和P5的宽度/长度(W/L)比的设计旨在降低IOUTPROT值,从而节省无用的电流消耗。此模块恰当工作的最小VIN是:

(2)

(2)

此最小输入电压值通过VSG_N6的值取决于IREXT。此值将会极高,因为事实上N6是具有高阈值电压的高压晶体管。晶体管P2的过驱动电压为0.3 V。

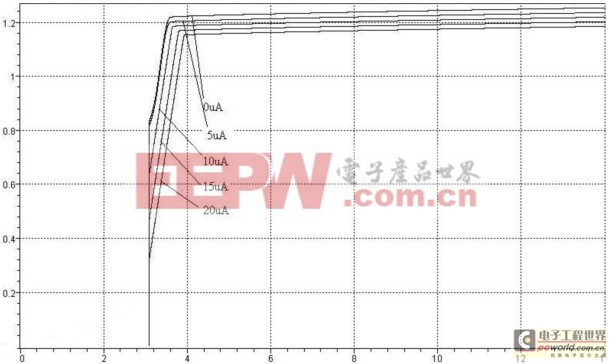

图3:IREXT = 0/5/10/15/20 µA时不同VIN下的VREXT仿真结果

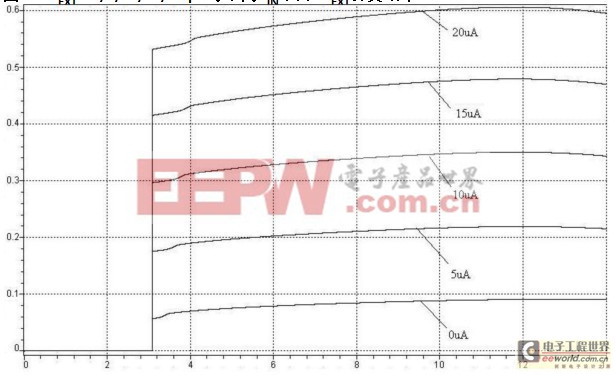

图4: IREXT = 0/5/10/15/20 µA时不同VIN下的LDO(RL = 0)的电流极限仿真结果。

电路分析

我们进行了一系列的高精度HSPICE电路仿真,从而验证所建议技巧的特性。图3显示了不同VREXT相对于VIN的波形,其中考虑到了IREXT的扫描幅度为0至20 μA,间隔为5 μA。电压VREXT需要相对于VIN及IREXT变化恒定。对于高于4 V甚至最高14 V的VIN而言,VREXT在任何IREXT值时都拥有良好的线路稳压性能,优于40 mV。如同预料,此图的拐点在某种程序上、但又并非在极大程度取决于IREXT电流电平。它介于3.4 V(0电流)与4 V(电流20 µA)之间。负载稳压(即VREXT相对于IREXT的变化)也不错,接近于80 mV。

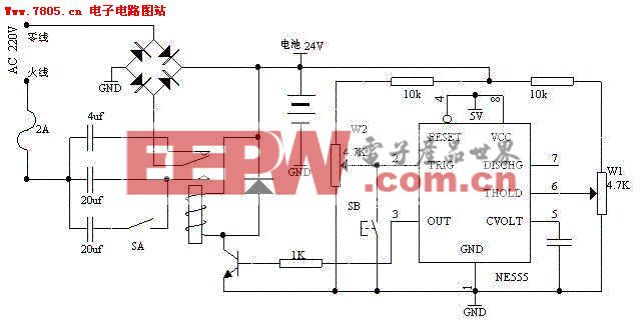

图4显示了LDO在不同VIN条件下的短路电流,其中顾及到了IREXT扫描。 对于零IREXT (无REXT)而言,电流极限低于0.1 A,并且随着VIN缓慢增加。短路电流值几乎随着IREXT线性增加。IREXT = 15 µA时,电流极限就为0.44 A至0.47 A,此电流电平等于0.3 A连续电流的应用而言是适宜的。相应地计算出REXT = 82 kΩ。IREXT = 20 µA时,电流极限已经极高,达0.54 A至0.605 A。就此建议的VIN范围为4 V至14 V。

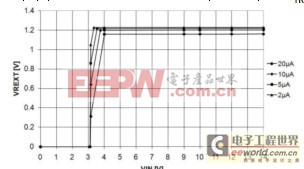

图 5: IREXT = 2/5/10/20 µA时不同VIN下的VREXT测量值。

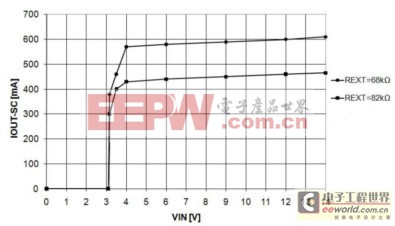

图6. REXT = 68 kΩ/82 kΩ时不同VIN下的IOUT-SC测量值。

测量结果

用于测试所建议技术的电路采用三层金属0.5 mm标准16 V CMOS工艺制造。此电路面积为1.3 mm2,其中包括用于使VADJ处于±1%目标精度范围内的微调电路。如前所述,建议的LDO输入电压范围为4 V至14 V,而参考电压为1.25 V。LDO的输出电压可以使用两颗电阻来在1.25 V与12 V之间外部设定。图5所示的是不同IREXT电流曲线下不同VIN时的VREXT,此图与图3所示的仿真图几乎相同。此外,线路稳压事实上更好,在VIN介于4 V至14 V的条件下,达到不超过3 mV。负载稳压也接近于仿真图中描绘的波形。图6显示了不同REXT值时在不同VIN下的LDO输出短路电流。

VOUT=6.5V (通过外部反馈网络获得)、REXT=82 kΩ及VIN=7 V时,满额1 mA至300 mA负载电流间隔、1 μs上升/下降时间时测得的瞬态负载稳压类似于图7,证明此电路工作速度相当快。

图7. 瞬态负载稳压测量结果:不同时间点时的IOUT及VOUT。

结论

应用如本文所述的外部控制技术来为LDO限流,为设计工程师提供了高度灵活性,让他们可以通过改变外部电阻值,从而为其特定电路设计选择最适合的电流。此额外引脚的电压通过连接至内部VREF的电压缓冲器来稳压。当REXT = 68 kΩ时,其电流高达0.6 A;但对于最大连续电流0.3 A的应用而言,最佳选择是将电流限制在最大0.45 A,而此电流极限可以通过使用阻值为82 kΩ的电阻REXT来获得。理论考虑、仿真及实验测试结果均显示了这种建议的外部控制技术能够完全发挥作用,而且LDO在满额1 mA至300 mA负载电流间隔时拥有极快速的瞬态响应。建议采用这种外部控制技术的LDO仅消耗100 μA电流(满载时为160 μA),300 mA电流时的压降为200 mV (VOUT=6.5V。

评论