数字电路设计中部分常见问题解析 2012-08-22

1 常见问题解析

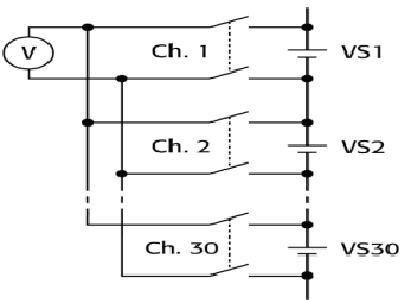

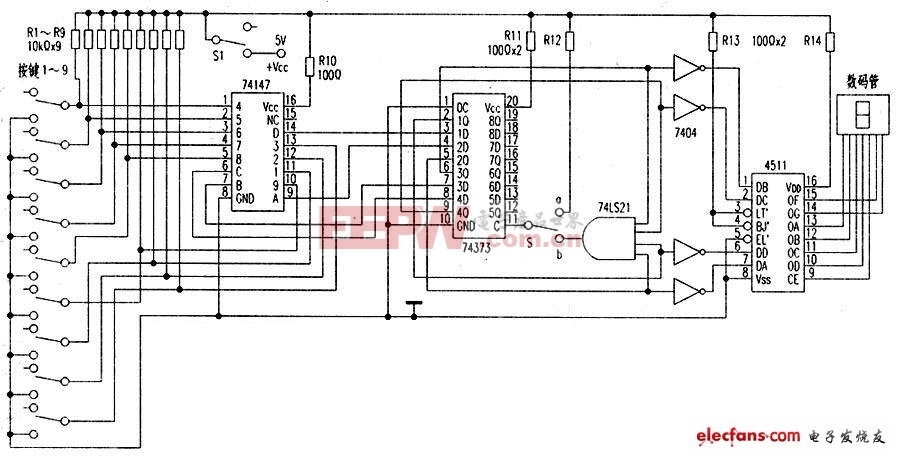

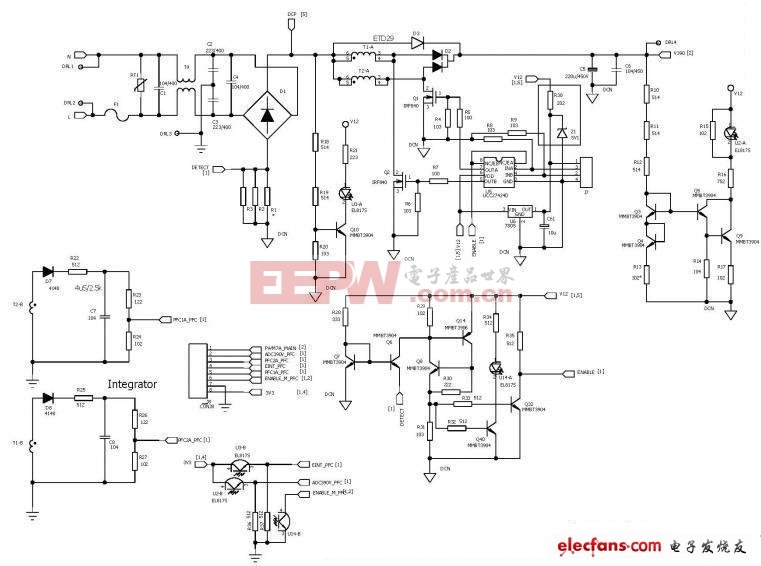

文中借助学生设计的双向(加减)计时器,如图1所示,来探讨电路设计中3个方面的常见问题。

则为“低有效”,即当该引脚为低电平时执行预置数动作或功能。

2)“同步”引脚

“同步”是指当该引脚处于有效电平时还不能即刻执行规定动作或功能,而必须等到时钟的有效沿到来时才可执行,即要与时钟的有效沿同步。

如另一种常用的计数器74LS161的第9引脚![]() 即为“同步”引脚,当它处于低有效电平时,还要等到时钟的有效上升沿后才能执行预置数动作或功能。

即为“同步”引脚,当它处于低有效电平时,还要等到时钟的有效上升沿后才能执行预置数动作或功能。

3)“异步”引脚

“异步”是指该引脚一旦处于有效电平则不必等到时钟CP的有效沿到来就即刻执行规定动作或功能,即可不与时钟CP的有效沿同步而为异步。

如74LS192的第14引脚(CLR)和第11引脚![]() 皆为“异步”引脚,一旦处于其有效电平时将即刻执行清零和预置数动作或功能。

皆为“异步”引脚,一旦处于其有效电平时将即刻执行清零和预置数动作或功能。

2 结束语

数字电路设计中常会遇到诸多问题,文中借助一个0~30 s双向(加减)计时器电路,采用例解形式对控制、时序、引脚等几个方面的常见问题进行了解析。

评论