数字签名算法SHA-1的FPGA高速实现(图)

随着网络的迅速发展,对安全性的需要越发重要。然而,尽管网络技术进步很快,安全性问题仍然相对落后,并且在很多情况下只能靠虚拟私人网vpn和防火墙。因虚拟私人网是构建在internet外部结构上的,必须采取某些措施保证安全性问题。一种方法是使用因特网协议安全性(ipsec)标准。ipsec是一组协议,它在ip协议层提供安全保密的通信。ipsec协议有通道和传输两种通信模式,为了保证在高速通信中的数据安全,在设计中使用硬件加速来实现ipsec中的加密和认证。ipsec中的加密部分使用三重des算法,或使用rc5、idea、blowfish和cast-128等算法作为加密手段。在ipsec协议中认证使用sha-1和md5单向散列函数算法实现,通过使用fpga高速实现sha-1消息认证算法。

sha-1算法介绍

安全散列算法sha(secure hash algorithm,sha)是美国国家标准和技术局发布的国家标准fips pub 180-1,一般称为sha-1。其对长度不超过264二进制位的消息产生160位的消息摘要输出,步骤如下。

首先填充消息使其长度恰好为一个比512的倍数仅小64位的数。填充方法是附一个1在消息后面,后接所要求的多个0,然后在其后附上64位的消息长度(填充前),使消息长度恰好是512位的整数倍。

5个32位变量,用十六进制表示初始化。然后开始算法的主循环,一次处理512位消息,循环次数是消息中512位分组的数目。

先把这五个变量复制到另外的变量中,a到a,b到b,c到c,d到d,e到e。

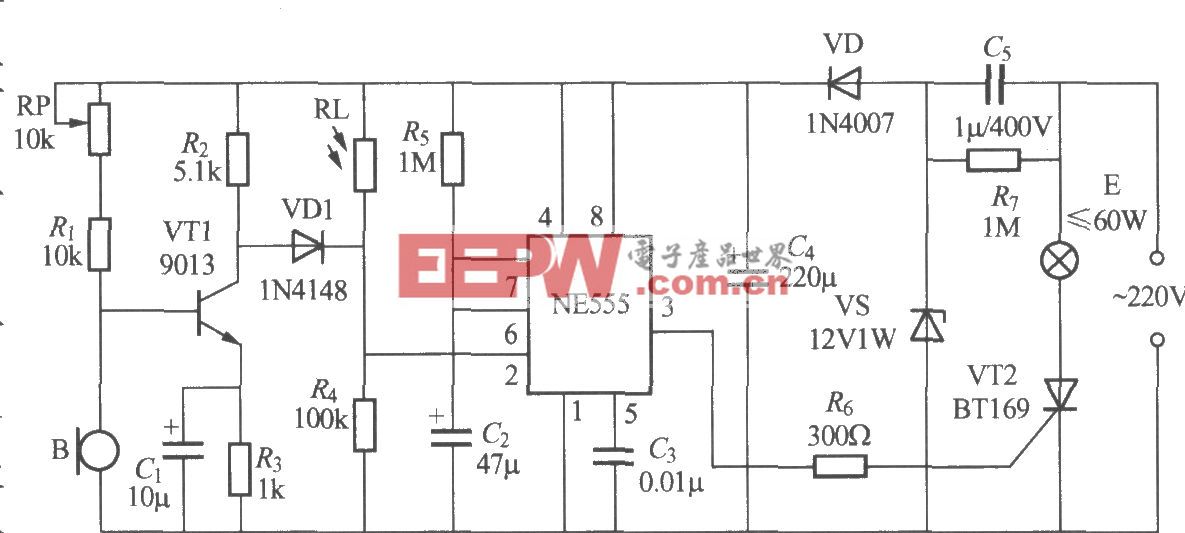

主循环有4轮,每轮20次操作,每次操作对a、b、c、d、e中的3个进行一次非线性运算,后进行移位和加运算,运算的过程见图1。a、b、c、d和e分别加上a、b、c、d和e,然后用下一数据分组继续运行算法。最后的输出由a、b、c、d和e级联而成。

sha-1算法的fpga实现

实现sha-1算法时,用软件先对消息进行预处理,使消息长度恰好是512位的整数倍,再以fpga实现对消息摘要计算的加速。

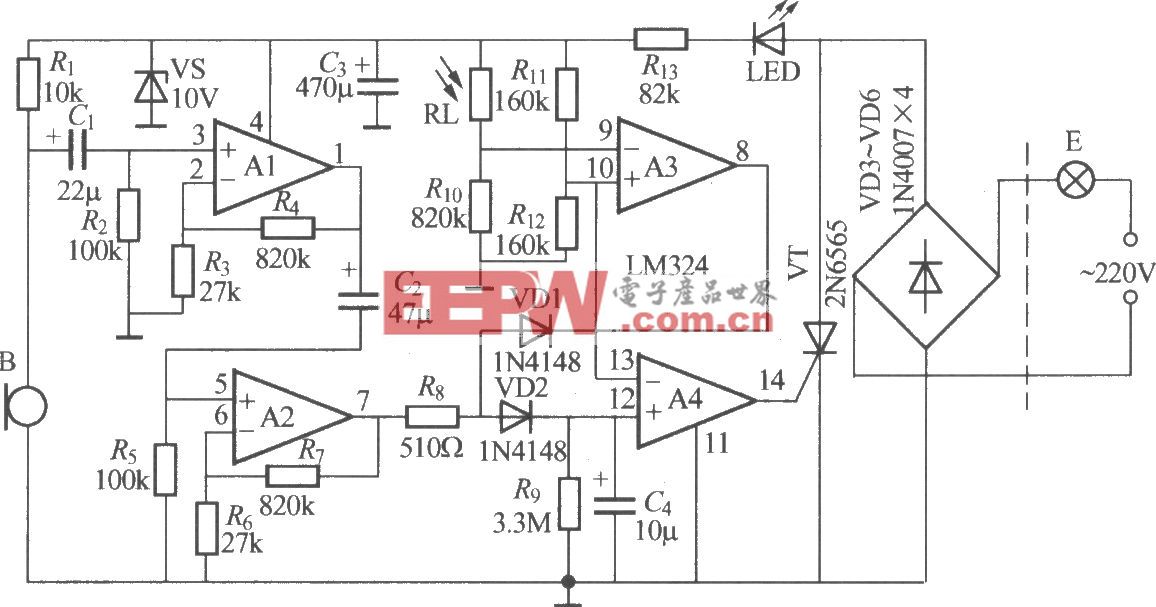

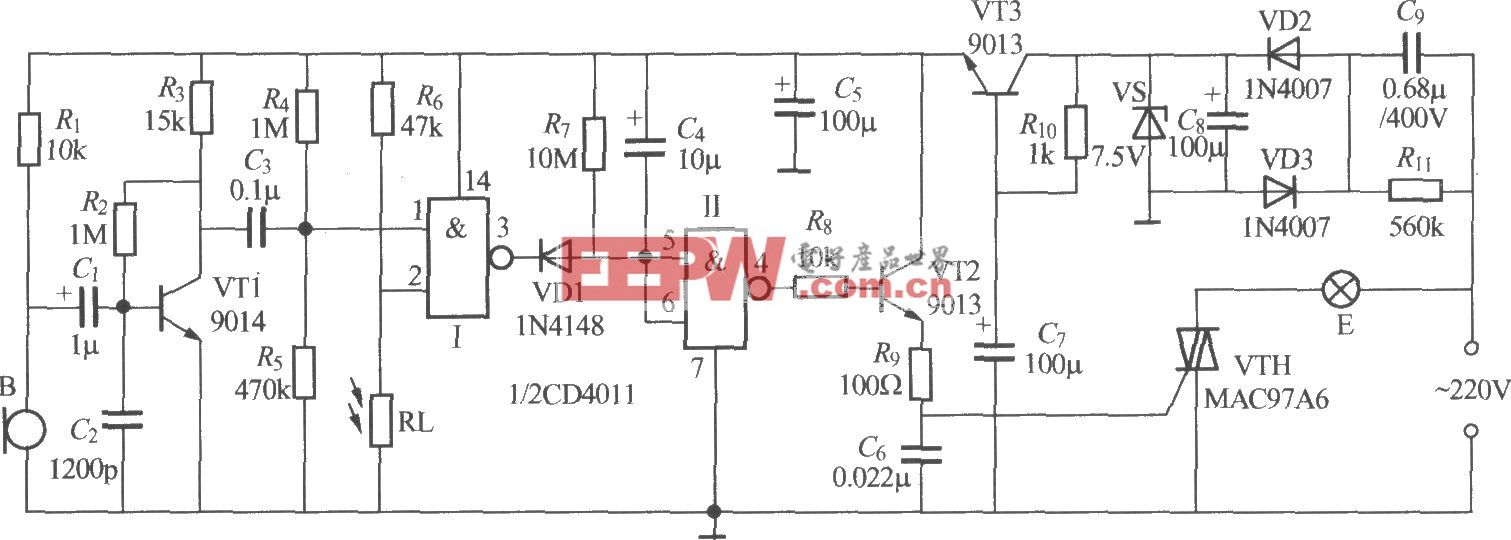

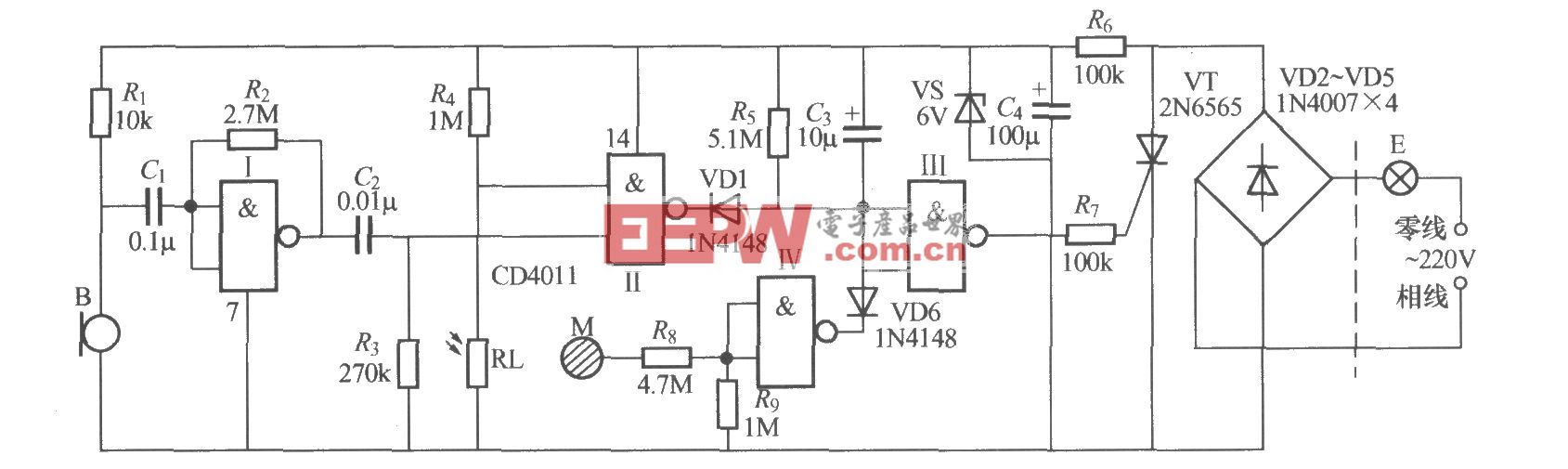

fpga的编程一般用verilog hdl或者vhdl进行,本设计采用了vhdl语言对sha-1算法进行描述。sha-1算法fpga加速器实现分为两大部分,分别是80个32位临时值wt(w0至w79)的生成,以及对32位临时值wt循环处理生成160位的消息摘要。图2为将子分组mj(0≤j≤15)变成80个32位wt(kt至w79)的电路框图,在设计时,用512位寄存器和2个多路选择器生成临时值wt(0≤t≤79)。

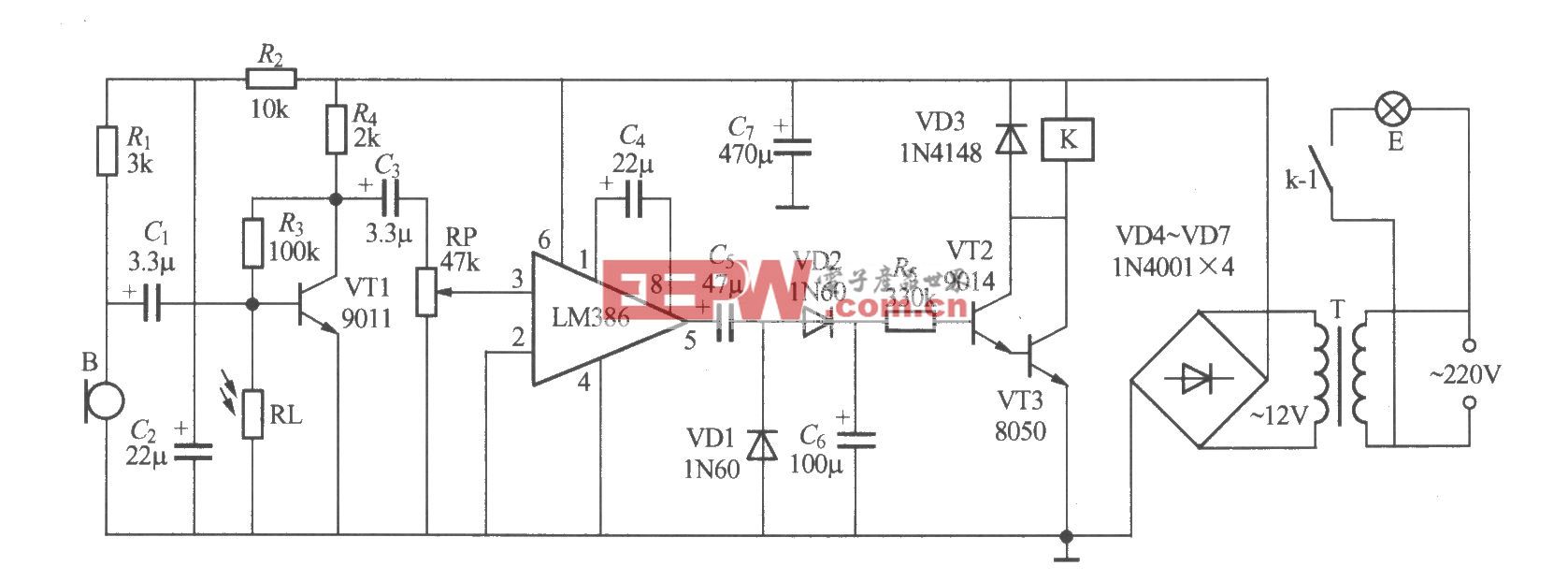

图3中160位输入数据缓冲器用来放置初始数据(5个32位变量a、b、c、d和e),而f1234代表sha-1算法中的4组非线性函数ft(x,y,z),根据需要用多路选择器mux-1选择其中一个(ft(x,y,z)=(x∧y)∨((x)∧z),对于t=0至19;ft(x,y,z)=x臲臵,对于t=20至39;ft(x,y,z)=(x∧y)∨(x∧z)∨(y∧z),对于t=40至59;ft(x,y,z)=x臲臵,对于t=60至79),4个常数为kt存在rom中(即组件),32

评论