基于CPLD的IEEE1149.1 USB下载电缆设计

引 言

随着片上系统(SoC,System on Chip)时代的到来,包括复杂可编程逻辑器件(CPLD,Complex ProgrammableLogic Devi(e)和现场可编程门阵列(FPGA,Field Programmable Gate Array)的可编程逻辑器件(具有在系统可再编程的独特优点),应用越来越广泛。这给用于可编程逻辑器件编程的下载电缆提出了更高的要求。

本文研究基于IEEEll49.1标准的USB下载接口电路的设计及实现。针对Altera公司的FPGA器件Cy-ckone,通过分析它的边界扫描测试结构和各种JTAG指令,研究它的编程过程和编程特点,并提出设计方案。在接口电路硬件设计中,选用FTDI公司的USB控制芯片FT2蛎BM,实现USB物理层和链路层协议的解析;Altera公司的可编程逻辑器件EPM7064实现接口逻辑。与传统的基于PC并口的下载电缆相比,本设计的USB下载接口电路具有支持热插拔、体积小、便于携带、降低对PC硬件伤害、编程速度快等明显优点。

目前已开发的USB下载线一般需要在主机端另行设计软件来控制与下载线及目标器件之间的通信和数据传送;但是这样不仅繁琐,而且可能由于PC机操作系统的不同而影响兼容性。本文讨论的USB下载线能在A1tera公司的QuartusII开发环境下直接使用,无须在主机端另行设计通信软件。

1 系统结构及工作原理

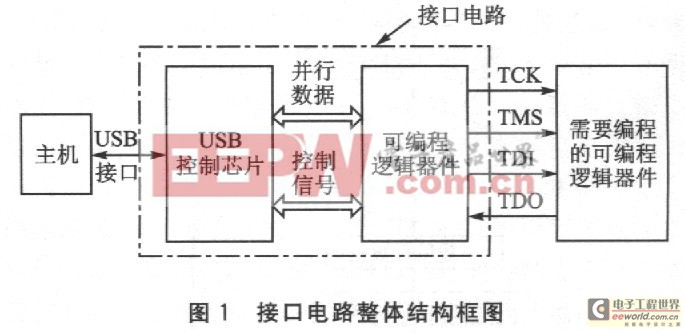

接口电路的整体结构框图如图l所示。由于USB下载电路涉及了IEEEll49.1标准和USB协议,所以接口电路主要包含两大部分。一部分是USB接口,它连接主机和可编程逻辑器件,主要功能是进行USB和并行I/O口之间的数据格式转换,用USB控制芯片实现。另一部分是JTAG接口,它连接USB控制芯片和需要编程的逻辑器件,主要功能是进行并行I/O口和JTAG之间数据的转换,转换逻辑通过对可编程逻辑器件进行设计来实现。其他还包括一些必要的时钟电路和电压转换电路。

从主机传来的USB数据,由USB控制芯片转换为8位并行数据,经数据总线送到CPLD的可编程I/O引脚。CPLD的数据也可以通过数据总线送回USB控制芯片,然后转换为USB的数据格式传回主机。CPLD收到USB控制芯片传送来的数据后,对数据进行解析,然后转换为符合IEEEll49.1标准的编程数据和指令,从TCK、TMS和TDI串行输出到要编程的可编程逻辑器件。从可编程逻辑器件返回的符合IEEEll49.1标准的校验数据从TDO串行输入到CPLD,转换为8位并行数据传送给USB控制芯片,最后返回主机进行校验。

评论