一种基于FPGA的NoC验证平台的构建

半导体工艺技术进入深亚微米时代后,基于总线系统芯片SoC(Svstem on Chip)的体系结构在物理设计、通信带宽以及功耗等方面无法满足未来多IP体系发展的需求。片上网络NoC(Netwotlk on Chip)是一种新的系统芯片体系结构,其核心思想是将计算机网络技术移植到系统芯片设计中来,从体系结构上彻底解决总线架构带来的问题。

研究人员从拓扑结构、路由算法、交换策略以及流控机制等多个方面对NoC进行研究,但是如何构建NoC验证平台,快速得到NoC的性能也一直是NoC研究的重点。

在过去的几年里,一些研究机构提出了对于NoC不同抽象层次的验证方法的研究,一般的NoC验证是基于软件的仿真和建模,如:用C、C++、SvstemC进行系统级建模仿真,这样验证很灵活,但在仿真时间上却开销很大。本文提出的基于FPGA的NoC验证平台在仿真速度方面是一般基于HDL的软件仿真的16 000倍,而基于PC机编写的NoC软件更增强了该平台的灵活性和实用性。

1 验证平台架构

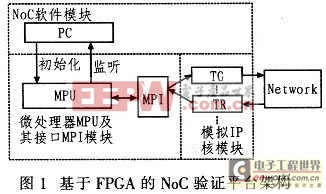

该验证平台采用模块化设计,可以很容易地对不同的NoC进行功能验证和性能评估。图1给出了该验证平台的基本架构。

它主要包括3个模块:

1)模拟IP核模块 该模块包含有数据流量产生器TG(Traffic Generator)模块及数据流量接收器TR(Traffic Receiver)模块。TG模拟产生NoC网络中各个IP节点可能产生的数据流量,TR用于收集NoC运行过程中的各种信息。TG/R作为一个IP节点和待测NoC中的每个交换节点相连接。

2)微处理器MPU及其接口MPI模块 PC机通过MPU(FPGA中自带的NiosⅡ软核)和MPI实现对NoC各IP核中TG内部各个配置寄存器的配置,并将TR中各个寄存器的内容读取到PC机中进行处理。本模块和模拟IP核模块构成FPGA硬件平台。

3)NoC软件模块 完成对NoC的配置以及NoC系统的性能统计。PC机通过MPU与FPGA进行通信,实现对NoC的配置并从FPGA中得到数据并进行后端处理,以图形的方式显示给用户,供用户对所设计的NoC进行评估。同时PC机可以监控NoC运行的情况。

FPGA采用Ahera公司Stratix IV系列中的EP4SGX230KF40C2,该器件能够提供高速的时钟信号和大量的片内资源,并具有大量外围接口电路可供使用,这为基于FPGA的验证提供了强有力的保证。

评论