基于FPGA的数字核脉冲分析器硬件设计方案

在此基础上通过电路设计建立了数字化能谱测量实验装置,实测了137Cs的能谱,测量结果与相同条件下的模拟能谱仪的实测谱完全吻合。由此证明基于FPGA的数字多道脉冲幅度分析器硬件设计方案的正确可行,具有实用性。

本文引用地址:https://www.eepw.com.cn/article/221558.htm0 引言

多道脉冲幅度分析仪和射线能谱仪是核监测与和技术应用中常用的仪器。20世纪90年代国外就已经推 出了基于高速核脉冲波形采样和数字滤波成型技术的新型多道能谱仪,使数字化成为脉冲能谱仪发展的重要方向。国内谱仪技术多年来一直停留在模拟技术水平上, 数字化能谱测量技术仍处于方法研究阶段。为了满足不断增长的高性能能谱仪需求,迫切需要研制一种数字化γ能谱仪。通过核脉冲分析仪显示在显示器上的核能谱 帮助人们了解核物质的放射性的程度。

1 数字多道分析仪的优势

国内很大一部分学者采用核谱仪模拟电路的方式实现脉冲堆积的处理。由于整个过程都是由模拟电路来实 现,所以一直受到多种不利因素的困扰:模拟滤波成形电路有限的处理能力达不到最佳滤波的要求;模拟系统在高计数率下能量分辨率显着下降,脉冲通过率低;模 拟电路固有的温漂和不易调整等特点,导致系统的稳定性、线性及对不同应用的适应性不高;在脉冲波形识别、电荷俘获效应校正等更复杂的应用场合模拟系统无法 胜任。

相比来看,数字脉冲幅度分析系统的性能显着优于模拟脉冲分析器。数字分析器有以下几点优点:通过软 件实现,提高了系统的稳定性与可靠性;可以利用数字信号处理方法针对输入噪声特点实现优化设计,达到最佳或准最佳滤波效果;处理速度快,反堆积能力强,相 同能量分辨率下脉冲通过率更高;参数由程序控制,调整方便、简单。

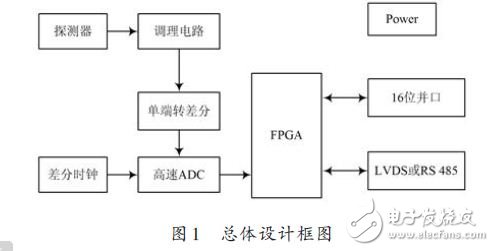

2 总体设计

本方案设计了一种基于可编程门阵列的多道脉冲幅度分析器的硬件平台。图1即为总体设计框图,探测器 输出的核脉冲信号经前端电路简单调理后,经单端转差分,由采样率为65 MHz的高速ADC 在FPGA 的控制下进行模/数转换,完成核脉冲的数字化,并通过数字核脉冲处理算法在FPGA内形成核能谱,核能谱数据可通过16 位并行接口传输至其他谱数据处理终端,也可通过LVDS/RS 485接口实现远程传输。特别需要注意的是,由于高速AD前置,调理电路应该满足宽带、高速,且电路参数能够动态调整的需要,以适应不同类型探测器输出的 信号,从而更好地发挥数字化技术的优势。

3 具体硬件设计

3.1 前端电路

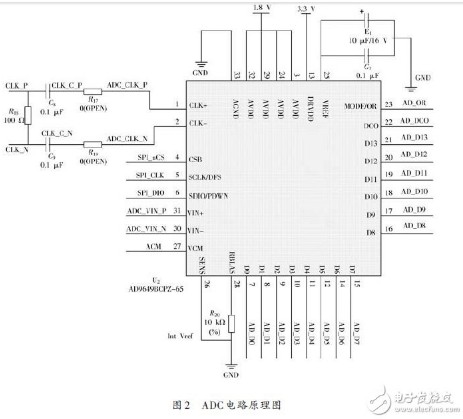

前端电路由单端转差分和高速ADC电路组成。差分电路由于其良好的抗共模干扰能力而应用广泛。由于 调理电路输出的脉冲信号为单极性信号,若直接送入ADC,将损失一半的动态范围。设计中在运放中加入一个适当的偏置电压,将单极性信号转换成双极性信号后 再送入ADC,以保证动态范围。将信号由单端转换成差分的同时,进行抗混叠滤波处理,完成带宽的调整 。

本设计使用AD9649 - 65 高速ADC 实现核脉冲的模/数转换,AD9649 为14 位并行输出的高速模/数转换器,具有功耗低、尺寸小、动态特性好等优点。当信号从探测器通过调理电路,过差分转单端电路后,以差分信号的形式进入ADC, 在差分时钟的控制下,转换成14 位数据,进入FPGA.该高速A/D 在外部FPGA 的控制下对信号进行采样。然后将采样后的数字信号送入FPGA 中实现数字核脉冲的幅度提取。图2 为A/D 转换的原理图,AD9649在差分时钟的同步下完成A/D转换,D0~D13为14个有效输出数据位。

3.2 FPGA

目前国内外多道脉冲幅度分析的数字化实现主要有2种方案:纯DSP方案、DSP+可编程器件方案。本文将充分发挥FPGA 的并行处理优势,在单片FPGA 芯片上实现核脉冲的采集与数字核脉冲处理算法,经Quar-tus-Ⅱ软件仿真与综合,本文选用EP3C40 FPGA芯片实现多道分析器的数字化功能。

fpga相关文章:fpga是什么

评论