适应多种时序的DMA控制器设计

1 图像协处理器的系统结构

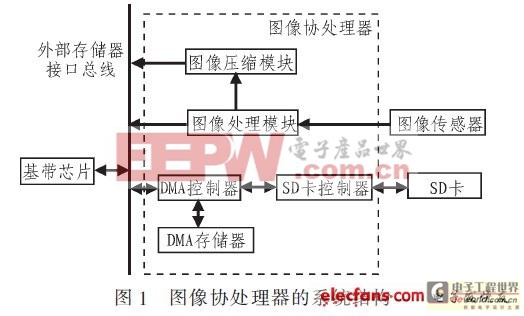

图1所示为该DMA控制器所处图像协处理器的系统结构,下面将对其的系统构成和数据流程做详细说明。

1.1 系统构成

基带芯片为移动终端设备的系统控制核心。其通过外部存储器接口总线(External eMI,Memory InteRFace bus)与该图像协处理器的控制端口相连。基带芯片不仅控制着图像协处理器所有模块的工作模式,而且负责图像数据的传送。EMI总线数据线宽度为16位,其控制的图像显示终端为分辨率为320x240的LCD。

图像传感器(sensor)为感光器件,其将接收到的光信号转为电信号,并在内部通过模拟/数字转换产生数字图像,在该图像协处理器设计中采用分辨率为640x480的图像传感器,其的工作时钟为24 MHz。

图像处理模块,即ISP(Image Signal Processing)模块被用于图像处理,包括去坏点、去噪声、边界增强等功能。

图像压缩模块被用于对图像处理模块输出的YUV422格式数据进行JPEG压缩。

SD卡控制器模块负责与SD卡的命令和数据交互,所有对SD卡的操作都由基带芯片配置SD卡控制器的相关寄存器完成。其与SD卡的接口包括CLK(SD卡的时钟信号线)、CMD(SD卡的命令线)、DATA0~DATA3(SD卡的4根数据线)。在与SD卡的数据交互中,一般是以block(512字节) 为单位的,并且在启动写卡命令之后,SD卡控制器必须在250 ms(SD version 2.0)内将所有数据写入SD卡中。

DMA控制器为基带芯片与SD卡控制器的接口模块,用于对写卡数据和读卡数据做暂时存储。其的本质功能是协调基带芯片和SD卡控制器之间的速度差异。存储数据的DMA存储器容量为5 120字节,即10个block数据。

1.2 数据流程

在该图像协处理器中,所有模块时钟频率均为48 MHz,其被2分频之后送至图像传感器,图像传感器以24 MHz频率送出格式为YUV422的640x480图像。

该图像协处理器有2种模式:图像预览模式和连拍模式。图像预览模式用于拍照前的图像预览,拍照者可以在LCD上看到将被拍下的图像。连拍模式用于连续拍摄图像,并将每一幅拍下的照片存入SD卡当中。

1.2.1 图像预览模式的数据流程

在图像预览模式下,图像传感器以24 MHz频率送出分辨率为640x480且格式为YUV422的图像,帧率为30帧/s。数据被48 MHz系统时钟同步后送入图像处理模块。图像处理模块将针对图像传感器的特点对图像进行处理以提高图像质量,然后将图像分辨率从640x480缩小至 320x240以适应LCD的显示分辨率,并将数据格式从YUV422转为RGB565。最后,基带芯片通过EMI接口将图像数据读出,直接写入LCD的显示缓冲区后在LCD上显示出来。

1.2.2 连拍模式的数据流程

当基带芯片启动连拍模式后,其首先配置图像传感器,使其以10帧/s的帧率送出分辨率为640x480的数字图像,数据格式仍然为YUV42 2。此时每帧的周期为100 ms,其中帧有效时间为30 ms,帧消隐时间为70 ms。

当数据送入图像处理模块后,该模块仍对图像进行处理并将图像分辨率从640x480缩小至320x240,之后将数据格式从YUV422转为RGB56 5。基带芯片也仍然通过EMI接口将该图像数据读出,并直接写入LCD的显示缓冲区中,这样在连拍的时候,仍可以在LCD上看到被拍下的图像。

图像处理模块在送出预览数据的同时也将320x240的YUV422数据送至图像压缩模块。为了兼顾压缩比和图像质量,一般配置压缩比在10:1左右,这样一幅320x240的图像经JPEG压缩后的数据量为320x240x2/10=15 360字节。为留出适当的备用空间,图像压缩模块将编码之后的数据存入一个容量为8 192x16位的存储器中,在此命名为JPEG_MEM。当一幅图像编码完成时,即在图像传感器进入帧消隐阶段之后,JPEG_MEM中已经存了一幅压缩之后的图像。随后图像压缩模块向基带芯片发出中断信号,基带芯片在从图像处理模块接收了当前预览图像的最后一部分数据并送LCD显示后,将响应该中

评论