- 时序约束的概念和基本策略时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE约束可以告诉综合布线工具输入信号在时钟之前什么时候准备好,综合布线工具就可以根据这个约束调整与IPAD相连的Logic Circuitry的综合实现过程,使结果满足FFS的建立时间要求。附加时序约束的一般策略是先附加

- 关键字:

FPGA 约束 时序

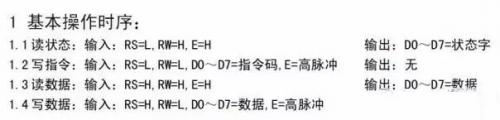

- 操作时序永远是使用任何一片IC芯片的最主要的内容,看懂时序图,再操控这个芯片就非常容易了。而提取芯片器件手册上有用的信息是使用芯片的最基本步骤。 以液晶显示芯片1602为例 首先我们来看1602的引脚定义,1602的引脚是很整齐的SIP单列直插封装,器件手册给出了引脚的功能数据表: 我们只需要关注以下几个管脚: 3脚:VL,液晶显示偏压信号,用于调整LCD1602的显示对比度,一般会外接电位器用以调整偏压信号,注意此脚电压为0时可以得到最强的对比度。 4脚:RS,数据/命令选择端,当此脚

- 关键字:

单片机 时序 LCD1602

- 一.概述:I2C 是Inter-Integrated Circuit的缩写,发音为eye-squared cee or eye-two-cee , 它是一种两线接口。I2C 只是用两条双向的线,一条 S

- 关键字:

I2C总线 时序 SDA SCL

- 简介控制器局域网络(CAN)可在多个网络站点之间提供强大的通信能力,支持多种数据速率和距离。CAN具有数据链路层仲裁、同步和错误处理等特性,广泛用于

- 关键字:

CAN接口 时序 CAN总线 CAN网络

- 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

- 关键字:

FPGA 时序

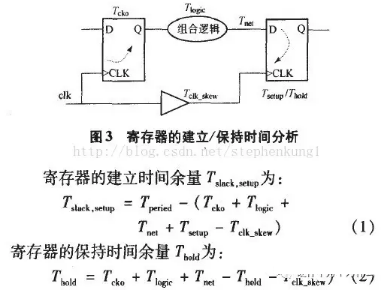

- 10、FPGA的时序基础理论 我们的分析从下图开始,下图是常用的静态分析结构图,一开始看不懂公式不要紧,因为我会在后面给以非常简单的解释: 这两个公式是一个非常全面的,准确的关于建立时间和保持时间的公式。其中Tperiod为时钟周期;Tcko为D触发器开始采样瞬间到D触发器采样的数据开始输出的时间;Tlogic为中间的组合逻辑的延时;Tnet为走线的延时;Tsetup为D触发器的建立时间;Tclk_skew为时钟偏移,偏移的原因是因为时钟到达前后两个D触发器的路线不是一样长。 这里我们来做如下转

- 关键字:

FPGA 时序

- 影响FPGA设计周期生产力的最大因素是什么?-提高FPGA设计生产力的工具、技巧和方法,9影响FPGA设计周期生产力的最大因素是什么?

- 关键字:

FPGA 时序

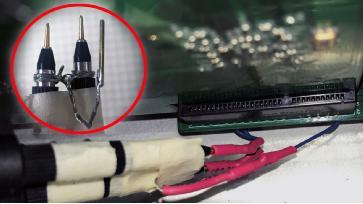

- 在某产品测试过程中,工程师反馈偶尔会出现数据异常,经过系统性的分析,致远电子测试团队推测可能是ADC芯片的SPI通信总线的时序存在偶发异常,但由于异常出现概率很低,该如何对SPI通信总线偶发的时序问题进行定位呢? 一、搭建测试环境 SPI总线测试点位于主机的主板底部,时钟频率大约为33MHz,属高频信号,所以对探头的端接方式比较讲究;为了方便测试,如图1所示,用短线将测试点引出,探头的地线也从前端自绕线引出,这样可以提高信号完整性,减少示波器采样对时序分析过程的影响。

- 关键字:

时序 SPI

- 交错ADC之间存在着多种不匹配的现象,如失调和增益不匹配。 此外,时序不匹配的校准方法也得到了工程师们的广泛关注。而在寻找解决方案之前,必须首先了解目前所面对的是什么,到底需要解决什么问题。 就像建筑工人

- 关键字:

交错杂散 时序

- 摘要:基于特种工业缝纫机应用范围的拓展,性能不断提升,要求自动缝制单元除有缝纫机自动缝制的功能外,同时兼有自动送料、自动折料、自动取料、自动定位功能。本文采用电控系统+外置可编程PLC实现要求功能,电控系

- 关键字:

自动缝制单元 电控系统 PLC 时序

- 摘要:为了提高LCD1602显示效果,增强抗扰能力,文章基于TOP2812开发板,依据LCD1602操作时序要求,在开发板CPLD部分实现了LCD1602显示系统的设计。文中对

- 关键字:

LCD1602 显示系统 时序 Vetilog HDL

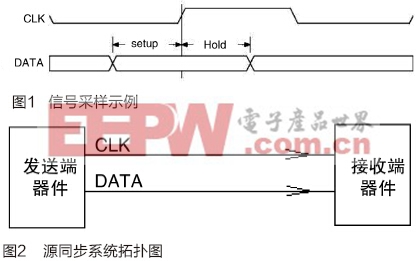

- 摘要:本文针对高速电路设计中经常面临的时序问题,提出了时序分析和计算方法,并结合SPI4.2接口给出了具体分析实例。

1 满足接收端芯片的建立/保持时间的必要性

在高速数字电路设计中,由于趋肤效应、临近干扰、电流高速变化等因素,设计者不能单纯地从数字电路的角度来审查自己的产品,而要把信号看作不稳定的模拟信号。采用频谱分析仪对信号分析,可以发现,信号的高频谱线主要来自于信号的变化沿而不是信号频率。例如一个1MHz的信号,虽然时钟周期为1微秒,但是如果其变化沿上升或下降时间为纳秒级,则在频谱仪

- 关键字:

DATA 源同步系统 数据类信号 时序 TSCLK 201412

- 写在coding之前的那些铁律

(1)注释: 好的代码首先必须要有注释,注释至少包括文件注释,端口注释,功能语句注释。

文件注释:文件注释就是一个说明文:这通常在文件的头部注释,用于描述代码为那个工程中,由谁写的,日期是多少,功能描述,有哪些子功能,及版本修改的标示。这样不论是谁,一目了然。即使不写文档,也能知道大概。

接口描述:module的接口信号中,接口注释描述模块外部接口,例如AHB接口,和SRAM接口等等。这样读代码的人即可能够判断即模块将AHB接口信号线转换成SRAM接口

- 关键字:

FPGA coding 时序

- 入门

结合一两个小项目把上面所说的事情都做好后,差不多就可以进入入门的阶段了(要求稍微严格了一点点,呵呵)。

入门阶段要学的有:设计时序;理解约束的原理及如何加约束。

先谈谈设计时序。

设计时序是进行逻辑设计的基本要求:时序是设计出来的,不是仿出来的,更不是凑出来的。

很多人在做逻辑设计时喜欢一上来就狂写代码,写到一半后发现信号间的时序出问题了,只好推倒重来;好不容易反复了几次之后,通过仿真软件看了下,差不多要对了,于是再凑一下时序,竟然对了!但这个做法除了设计周期长外,

- 关键字:

逻辑设计 时序 约束

- 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些小技巧和帮助来设置时钟;使用像Synopsys Synplify Premier一样的工具正确地设置时序约束;然后调整参数使之满足赛灵思FPGA设计性能的目标。

会有来自不同角度的挑战,包括:

● 更好的设计计划,例如完整的和精确的时序约束和时钟规范

● 节约时间的设计技术,例如为更好的性能结

- 关键字:

FPGA Synplify 时序

时序介绍

您好,目前还没有人创建词条时序!

欢迎您创建该词条,阐述对时序的理解,并与今后在此搜索时序的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473