基于FPGA和单片机的多功能计数器设计

一、系统方案

方案1:采用中小规模数字电路构成系统,由计数器构成主要的测量模块。用定时器组成主要的控制电路。此方案软件设计简单,但外围芯片过多,且频带窄,实现起来较复杂,功能不强,而且不能程控和扩展。

方案2:采用单片机实现。被测信号经调理后送入单片机,利用其内部的计数器完成计数,然后再进行数据处理和显示,但单片机在处理高速信号时略显吃力。

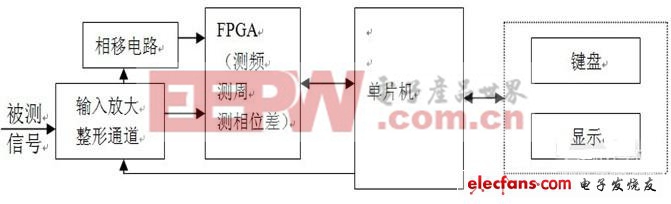

方案3:利用FPGA对调理后的被测信号实现高速计数,单片机软件执行高精度浮点数运算并显示。单片机完成系统的数据处理、逻辑控制和人机交互功能;大规模现场可编程器件(FPGA)实现外围计数功能。电路框图如图1所示。

图1 方案3系统框图

方案比较与选择:方案1 采用中小规模集成电路来实现,系统电路较复杂,扩展性能差;方案2用外围电路配合单片机实现测量功能,信号频率比较高时需外加分频电路,影响测量精度和系统稳定性,且单片机任务繁重,给软件设计和调试工作带来不便;方案3用一片高度集成的可编程逻辑器件可完成有关电路所有模块的设计,大大降低了电路复杂度,减少引线信号间的干扰,提高电路的可靠性和稳定性。加上单片机控制,应用单片机的数学运算和控制功能,辅以有效的软件滤波算法,能够进一步提高测量精度,且控制灵活、易于扩展和调试简单,能够达到题目要求。故本设计采用方案3,系统框图如图1所示。

二、理论分析与计算

1、频率和周期测量方法分析

由于频率和周期之间存在倒数关系(f=1/T),所以只要测得两者中的一个,另一个可通过计算求得。

1)直接测量法 对测频在低频端1Hz时,若闸门时间为1s,其 ±1量化误差大到100%。为了满足测试精度的要求,显然不能采用直接测量法;

2)直接与间接测量相结合的方法 需对被测频率和中界频率的关系进行判断,在中界频率附近仍不能达到较高的测量精度;

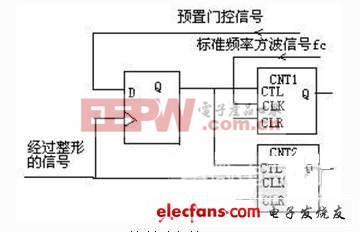

3)等精度测量法 图2为等精度测频、测周原理方框图。

图2 等精度测频原理图

2 相位差测量方法分析

相位差的测量有很多种方法,如相位—电压转换法、数值取样法和相位差—时间转换法等。其中相位差—时间转换法实际上是测量两个正弦信号波形上两个相应点之间的时间间隔t,若两被测信号周期均为T,则时间间隔t对应的相位差为:

如果只测量一个周期的t和T,无法满足宽频带被测信号的测量精度。如果时间间隔t和周期T测量值比较准确,再通过单片机对实测数据进行高精度浮点数运算及误差修正,就可以达到精度要求。按照这一思路,结合上面对等精度测频、测周原理及误差的分析可知,此方法是切实可行的。

设门控信号的开启时间为tc ,计数值为N,则tc=NT0 (5)

式中T0 为时标信号的周期,由(5)式和(6)式得

式中f为被测信号频率,10HZ≤f≤100kHZ ,f0 为标准时基,N为计数值。

3 宽带通道放大器分析

因为三极管放大电路参数选择复杂,低频特性不好,抗噪性能差。因此,设计中采用了宽频带、低噪声、高输人阻抗的运算放大器组成高精度放大电路,以获得良好的频率特性和抗干扰能力。输入通道中的放大级设计主要考虑增益和带宽的指标。题目要求能够测量信号幅度峰值范围约为14mv~7.07v。这个范围是比较宽的,既涉及到小信号放大,又要考虑比较器输入电压限制问题,因此,应根据信号幅度大小分段选择放大器的增益。还有就是要满足运放增益带宽积的要求。

三、电路与程序设计

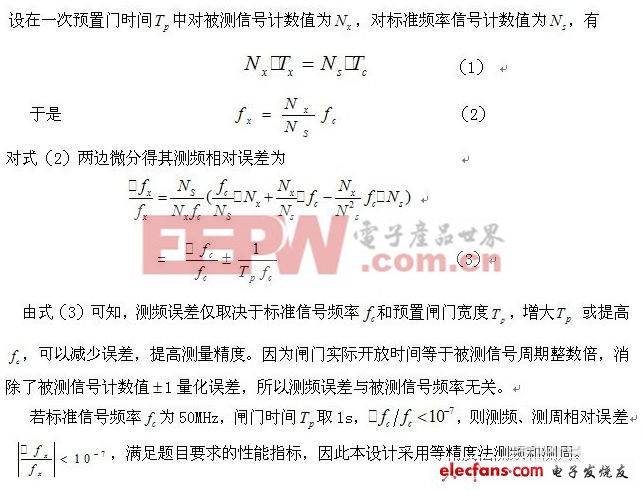

1 输入通道电路设计

待测频率信号由于衰减、传输干扰等原因,不能直接用于测量,需要经过处理后才能适合逻辑控制器的输入。输入通道组成框图如图3所示。

图3 输入通道组成框图

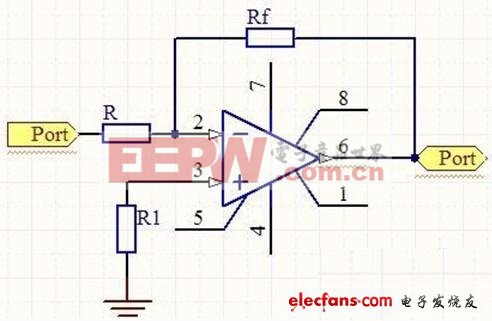

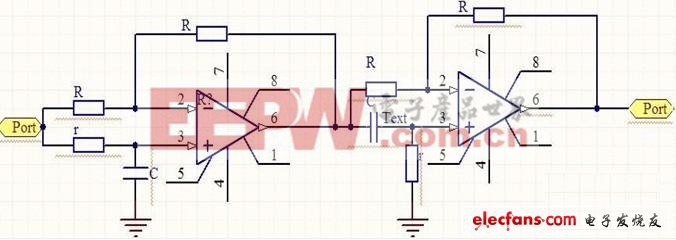

图4 放大电路原理

输入信号经电压跟随器缓冲后进入放大通路,灵敏度控制采用单片机控制继电器的通断来选择不同的放大倍数,被放大的信号经比较器输出与被测信号同频率的方波计数信号若要测相位差,则同频信号经放大后进入移相网络,然后经过零比较得到移相后的计数信号。

比较器采用滞回接法,详细电路见附录一,从而避免了过零点信号的毛刺造成整形信号的误翻转。其中放大电路基本原理如图4所示,其中Rf为反馈电阻,R为输入端电阻,有

Uo = - Ui × ( Rf / R ) (7)

由式(7)知,调节Rf的大小即可调整电路的增益。

移相网络电路如图5所示。

图5 移相网络电路图

图6 FPGA功能实现框图

对图5电路分析知,两级网络的振幅特性均为A(ω)=1 ,前级网络相频特性为

可见此为超前网络;后级网络相频特性为

所以相位发生滞后,通过改变阻值r即可实现相移量调整。两级级联后移相范围为0~360°。

2 FPGA 功能实现模块

FPGA实现部分主要分为信号同步处理,等精度计数和数据处理及传输3部分,如图6所示。FPGA采用Altera公司的EP2gC5Q208C8,经分析知能够实现题目要求。

(1) 同步处理电路 待测信号从外时钟域进入,属于异步信号,对测量精度乃至整个系统的稳定都有很大的影响,在这里,先对输入信号进行一次采样进行消抖,滤去可能存在的毛刺, 然后进行一级同步处理,尽可能有效地对异步信号进行同步处理。

(2)计数测量 采用等精度法测频率,利用相位~时间转换法进行相位差测量,并将测得数据进行寄存。

(3) 数据存储 将得到的并行数据转换为串行数据 再通过时序控制将数据写入双口RAM,然后单片机以其自身的时钟频率进行读取,从而有效地消除跨时钟域数据处理时所造成的不稳定影响。.

3 单片机控制模块

在本系统中,单片机采用MSP430F149,主要完成放大通路灵敏度选择、读取实测数据及处理和键盘与显示接口等三种功能。其中灵敏度选择是通过控制继电器的通断来实现通路切换;按键采用红外遥控方式,其中发射部分采用 PT2221,接收部分采用高灵敏度、高度集成的一种新型红外遥控接收光电模块HS0038,然后通过单片机直接软件解码处理,进而执行与之对应的中断服务子程序;因为要同时显示较多数据,所以我们采用字符型液晶显示。

4 主程序流程图

单片机系统主要流程图如图7所示,具体程序见附录三。

fpga相关文章:fpga是什么

手机电池相关文章:手机电池修复

单片机相关文章:单片机教程

单片机相关文章:单片机视频教程

单片机相关文章:单片机工作原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理 双控开关相关文章:双控开关原理

评论