CXL、CCIX 和 SmartNIC 下的 PCIe 5 将如何影响解决方案加速

与普通的 NIC 不同,SmartNIC 将会对 PCIe 总线提出更高的要求。CXL 和 CCIX 等第五代 PCIe 和协议在此背景下应运而生。不久之后,我们将能共享一致性存储器、高速缓存,并建立多主机点对点连接。

本文引用地址:https://www.eepw.com.cn/article/202011/420681.htm

正文:

过去三十年间,基于服务器的计算历经多次飞跃式发展。上世纪 90 年代,业界从单插槽独立服务器发展到服务器集群。紧接着在千禧年,产业首次看到双插槽服务器,再后来,多核处理器也问世了。进入下一个十年,GPU 的用途远远超出了处理图形的范畴,我们见证了基于FPGA的加速器卡的兴起。

随着迈入 2020 年,网络接口卡( SmartNIC ),也即数据处理单元( DPU )开始风靡。它们大量采用 FPGA 或多核 Arm 集群或是两者混搭,每种做法都能大幅提高求解性能。从股票交易到基因组测序,计算正在以更快的速度求解答案。在机箱内部,数据通道是 PCI Express( PCIe )。虽然几经变革,但它仍然是无可争议的选择。

PCIe 的演进发展

高速外围组件互连( PCIe )于 2003 年首次亮相,恰逢网络准备开始从以千兆位以太网( GbE )为主要互联的时代向更高网速的时代跃进。此时,Myrinet 和 Infiniband 等高性能计算( HPC )网络刚刚超越 GbE,数据速率分别达到 2Gb/s 和 8Gb/s。此后不久,10-GbE 网络接口控制器( NIC )崭露头角,而且性能优异。它们在每个方向上的速率接近 1.25GB/s,这种 8 通道( x8 )PCIe 总线的诞生恰逢其时。

第一代 PCIe x8 总线在每个方向上的速率为 2GB。当时 16 通道( x16 )的插槽尚未问世,服务器主板一般只提供一些 x8 插槽和几个 x4 插槽。为了节省成本,部分服务器厂商甚至使用了 x8 连接器,但却仅将它们连接成 x4,这确实十分有趣。

大部分人(像我一样的架构师)都知道,PCIe 每发展一代,速度就会提高一倍。今天的第四代 PCIe x8 插槽的速率大约为 16GB/s,因此,下一代速率将在 32GB/s 左右。如果第五代 PCIe 皆能达到这一水平,那确实也不错。不过它还像阿拉丁神灯那样神奇,能以 CXL 和 CCIX 两种新协议的形式允诺在 CPU 与 SmartNIC 或协处理器等加速器之间实现高效的通信。

CXL

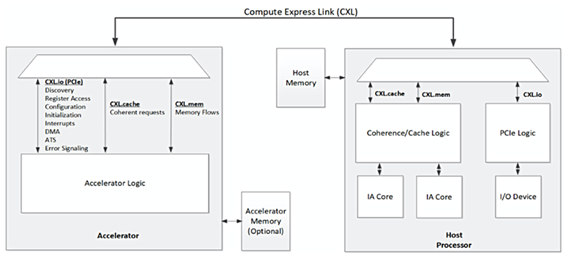

我们先谈 CXL。它提供了定义清晰的主从模式。在这种模式下,CPU 的根联合体能通过与加速器卡的高带宽链接来共享高速缓存和主系统存储器(图 1)。

1. 通过 CXL 与处理器相连的加速器的概念图。(来源:Compute Express Link Specification July 2020,0.9 版第 2 次修订,第 31 页)

这有助于主机 CPU 高效地向加速器分派工作并接收处理结果。部分此类加速器使用 DRAM 或高带宽存储器( HBM )来配备大容量高性能本地存储器。借助 CXL,现在可将这些高性能存储器与主机 CPU 共享,从而更便捷地在共享存储器中处理数据集。

此外,对于原子事务,CXL 能在主机 CPU 和加速器卡之间共享高速缓存存储器。CXL 在改善主机与加速器间的通信方面有了长足的发展,但未能解决 PCIe 总线上的加速器之间的通信问题。

2018 年,Linux 内核最终加入了可支持 PCIe 点对点( P2P )模式的代码。从而更方便在 PCIe 总线上的不同设备之间共享数据。虽然 P2P 早在本次内核更新前就已经存在,但它需要精心调试才能运行,往往要求用户能够通过编程就对等设备进行控制。更新内核后,加速器与 PCIe 总线上的 PCIe/NVMe 存储器或另一个加速器间的通信方式相对简化。

随着解决方案变得日益复杂,简单的 P2P 已不敷使用,而且会成为解决方案性能的制约因素。今天我们使用 DIMM 插槽中的永久存储器、NVMe 存储和直接插在 PCIe 总线上的智能存储( SmartSSD ),配以各种加速器卡和 SmartNIC 或 DPU(其中一些本身就具有很大的存储容量)。由于在这些设备之间必须实现通信,因此我们昂贵的服务器处理器将化身为成本高昂的流量灯,并且成为海量数据流的瓶颈。CCIX 在此情形下就能大显身手了,其环境适合在 PCIe 总线上的设备之间建立对等关系。

加速器缓存一致性互联

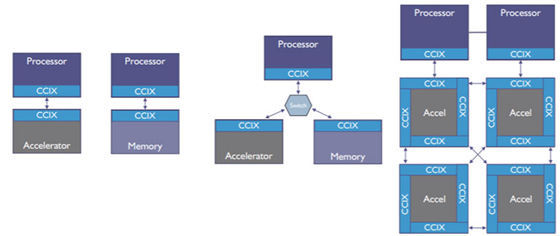

有人认为 CCIX 标准与 CXL 大同小异,但事实并非如此。在实现总线上点对点连接方面,CCIX 的方法与 CXL 截然不同(图 2)。此外,它还能利用不同设备上的存储器,每个设备具有不同的性能特征,对这些存储器进行池化,并映射到单一的非统一存储器访问 (NUMA) 架构。随后它建立 Virtual Address 空间,使池中的所有设备都能访问 NUMA 存储器的完整范围。这已经远远超出简单的 PCIe P2P 存储器间复制或是由 CXL 实现的主从模式。

2. 三种样本 CCIX 配置包括直接附加、交换拓扑和混合菊花链。(来源:An Introduction to CCIX White Paper,第 5 页)

作为一种概念,NUMA 自上世纪 90 年代以来一直存在,所以业界对它的理解也十分深入。以此为基础,当今的大多数服务器都能轻松地扩展到太字节( TB )或更大容量的 DRAM 存储器。不仅如此,能映射名为永久存储器(PMEM)或存储级存储器( SCM )的新型存储器的驱动程序业已存在,它能与真实存储器搭配,创建“海量存储器”。综合运用 PCIe 5 和 CCIX,将会进一步帮助系统架构师利用 SmartSSD 扩展这一概念。

计算存储

SmartSSD 也叫计算存储,它将计算器件(通常为 FPGA 加速器)与固态驱动器中的存储控制器紧密布局,或在控制器中嵌入计算功能。从而使 SmartSSD 中的计算器件能够在数据出入驱动器的过程中处理数据,进而重新定义数据的访问和存储方式。

虽然 SmartSSD 最初被视为块设备,但在 FPGA 中安装适当的未来驱动程序后,可以当作可按字节寻址的存储使用。现今生产的 SmartSSD 有数太字节的容量,而且容量还会暴增。因此,只有通过 NUMA,SmartSSD 才能用于扩展大容量存储器概念,这样一来主机 CPU 和加速器应用就能跨大量设备访问数太字节容量的存储器,且无需使用该存储器重新写入应用。此外,通过实现内联压缩与加密,SmartSSD 还能提供更佳的 TCO 解决方案。

引入 SmartNIC

具体该如何使 SmartNIC 与该架构匹配呢?SmartNIC 是一种特殊类型的加速器,位于 PCIe 总线和外部网络之间的连接处。SmartSSD 将计算放在紧挨数据的位置上,而 SmartNIC 则让计算紧临网络。为什么这一点如此重要?简单地说,我们很少关注服务器应用自身的网络时延、拥塞、丢包、协议、加密、叠加网络或安全政策等问题。

为了解决这些问题,创建了 QUIC 等低时延协议,用于改善时延问题、缓解拥塞,以及实现丢包恢复。我们已经开发出了 TLS 并采用内核 TLS(kTLS)加以扩展,以加密运行中的数据,保障数据安全。我们现在看到正在将 kTLS 当作 SmartNIC 的一项卸载功能添加进来。

为了支持虚拟机(VM)和容器的编排,我们创建了叠加网络。随后又开发出 Open vSwitch( OvS )等技术,用于对叠加网络进行定义和管理。SmartNIC 正在开始卸载 OvS。

最终,我们按照政策进行管理以确保安全。这些政策有望反映在 Calico 和 Tigera 等形式的编排框架中。这些政策很快也将通过使用 P4 等编程匹配动作框架被卸载到 SmartNIC。所有这些任务都应该卸载到名为 SmartNIC 的这类专用加速器上。

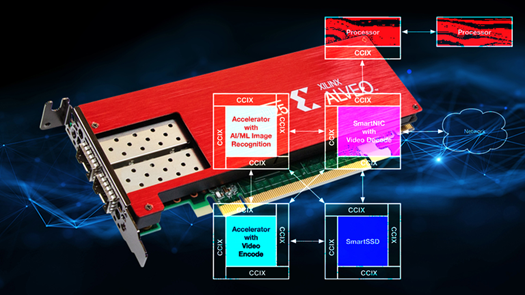

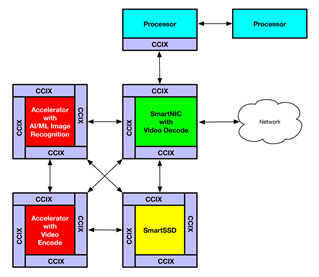

借助 CCIX,架构师可以构建出一个解决方案,作为有单一虚拟地址空间的单个超量存储器空间,使多个加速器直接访问真实存储器和 SmartSSD 中的存储。例如,可使用四个不同的加速器来构建解决方案(图 3)。

3. 图中所示的是样本 CCIX 应用,它使用了修改的 CCIX 4c-混合菊花链模型。

SmartNIC 能加载视频解码器,视频从摄像头导入后,就能转换回未经压缩的帧,存储在 NUMA 虚拟地址空间的共享帧缓存中。在这些帧可用后,运行在人工智能( AI )图像识别应用上的第二个加速器能扫描这些帧,识别人脸或车牌。与此同时,第三个加速器可以对这些帧进行转码,用于显示和长期存储。最后,运行在 SmartSSD 上的第四个应用负责在 AI 和转码任务成功完成后从帧缓存中删除这些帧。这里我们用四个高度专业的加速器协作运行,形成所谓的“Smartworld”应用。

行业开始添加了更多内核,以解决与摩尔定律相关的问题。如今,虽然内核的数量相当充裕,但 CPU 与 NIC、存储和加速器等外部器件间的带宽不足。PCIe Gen5 是我们的下一个关键发展点。它能大幅提高带宽,开启在 CPU 上进行高性能计算的时代。

例如,典型的 CPU 核心能处理 1Gb/s+,如果你采用双 128 核 CPU,那么 PCIe Gen4x16 是不够用的。对于需要在 CPU 核心和加速器之间进行密切交互的应用来说,CXL 和 CCIX 协议提供的高速缓存一致性具有诸多优势。数据库、安全性和多媒体等主要应用工作负载现在正开始利用这些优势。

编排

这个问题的最后一个环节是编排。这项功能指 Kubernetes 等框架能自动发现并管理加速硬件,并在编排数据库中将其标记为在线可用。它随后还需要知道该硬件是否支持上述一个或多个协议。随后,随着新求解实例请求的进入以及动态启动,能够由这些高级协议感知并加速的容器实例就可以使用该硬件。

赛灵思已开发出赛灵思资源管理器(XRM),能够与 Kubernetes 协同工作,管理池中的多个 FPGA 资源,从而提升加速器的整体利用率。这样一来,就能自动分派新发布的应用实例,使其在基础设施中最适当的高性能资源上执行,同时遵守既定的安全政策。

SmartNIC 和 DPU 使用了 PCIe 5 和 CXL 或 CCIX,将为我们提供高度互联的加速器,有助于开发复杂、高性能的解决方案。这类 SmartNIC 将在我们的数据中心内乃至整个世界范围内,向其他系统提供计算密集型连接。甚至可以构想这样一个未来:命令一旦进入 Kubernetes 控制器,就在 SmartNIC 资源上以原生运行的方式启动容器或 POD。这个新工作负载的大量计算随后可能会在服务器中某处的加速器器件上进行,甚至完全不需要服务器主机 CPU 的直接参与。

要正确发挥这样的功能,我们就需要进一步强化安全,使安全水平远远高于 Calico 和 Tigera。此外,我们也需要新的加速器感知安全框架来将安全环境(通常称为安全飞地)扩展到多个计算平台上。这样就使得 Confidential Computing 有了用武之地。它应该同时提供所需架构和 API,从而为单个安全飞地内多个计算平台上的在用数据提供保护。

所有敏感信息隔离设施(SCIF)都是如此。计算机中的安全飞地应能覆盖多个计算平台,而激动人心的时刻就在眼前。

评论