如何识别和防止7nm工艺失效

器件的良率在很大程度上依赖于适当的工艺规格设定和对制造环节的误差控制,在单元尺寸更小的先进节点上就更是如此。过去为了识别和防止工艺失效,必须要通过大量晶圆的制造和测试来收集数据,然后对采集到的数据进行相关性分析,整个过程费时且昂贵。如今半导体虚拟制造工具(例如SEMulator3D®)的出现改变了这一现状,让我们可以在“虚拟”环境下完成以上实验。甚至在硅材料中进行工艺实验之前,虚拟制造就可以用于了解工艺之间的相互影响和工艺步骤灵敏度以实现最大化良率。本文将通过一个简单示例来演示如何通过虚拟制造来提升7nm节点特定结构的良率,其中使用到的技术包括失效分类、良率预测和工艺窗口优化。

本文引用地址:https://www.eepw.com.cn/article/202008/417311.htm良率提升与失效分类

A. 失效分类定义

边缘定位误差是导致后段制程良率损失的主要失效模式[1]。下面用简单实例说明,假设M1由金属A(MA)和金属B(MB)组成【通常由LELE(光刻-刻蚀-光刻-刻蚀),或自对准双重图形化技术(SADP)工艺产生】,而接触孔(VC)被设计连接到MB。

金属关键尺寸CD(或SADP工艺中的心轴CD)或VC CD或金属至VC的套准精度存在工艺误差,会引起因通孔和金属层之间产生边缘定位误差而导致的良率损失。

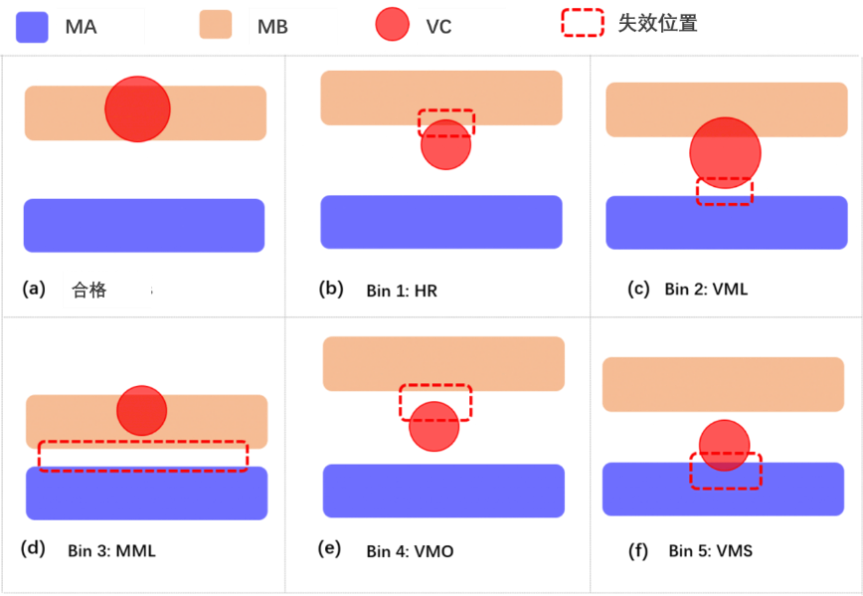

如下失效分类分别对应不同的CD和套准误差组合(见图1):

1、 高接触电阻(HR):VC和MB接触面积过小

2、 VC-MA漏电(VML):VC至MA的距离过小

3、 MA-MB漏电(MML):MA至MB的距离过小

4、 VC-MB开路(VMO):VC未接触MB,两者之间没有重叠

5、 VC-MA短路(VMS):VC接触MA,两者之间有部分重叠

图1. 分类图示(a)合格,(b)HR,(c)VML,(d)MML,(e)VMO,(f)VMS

B. 结构构建与校准,以及失效模式生成与识别

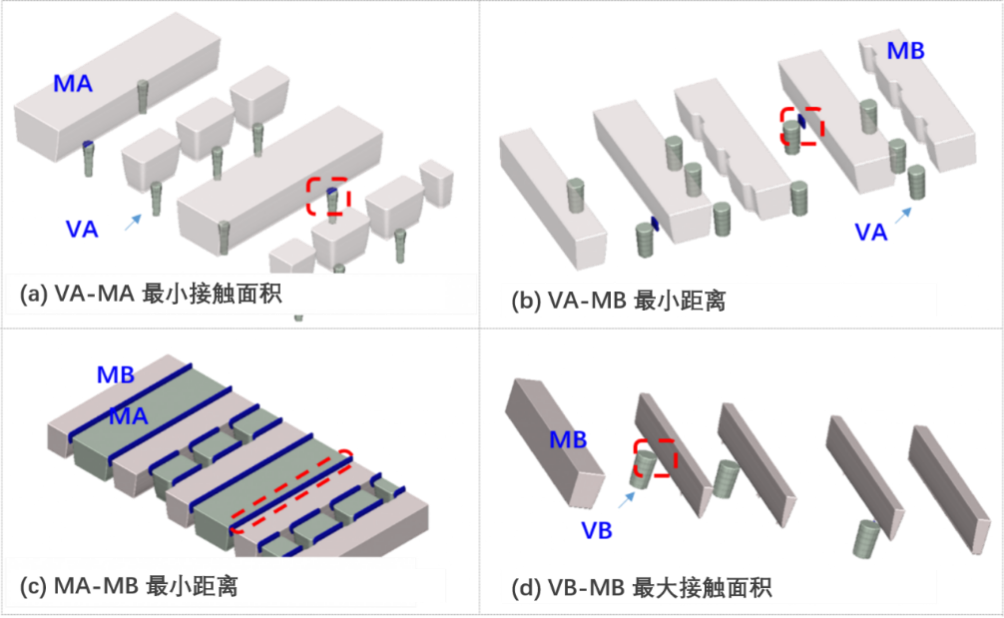

为了演示如何通过虚拟制造提高良率,现构建一个7nm的 VC和M1工艺。在生成并校准虚拟工艺结构之后,执行一系列虚拟量测步骤。图2展示了在虚拟结构上相应的测量位置,根据测量结果,可以将当前失效纳入相应的失效分类。

基于特定的规格和规则,可以根据测量结果自动实现失效模式分类。

图2 虚拟测量(结构检索)(a)VA-MA最小接触面积,(b)VA-MB最小距离,(c)MA-MB最小距离,(d)VB-MB最大接触面积

C. 良率预测和失效模式排行

在实际的制造过程中,心轴/通孔 CD和套准精度等工艺参数被控制在以目标值为中心一定宽度的范围内分布。通过SEMulator3D可自动执行实验设计(DOE)并生成和收集由用户定义的平均值和范围宽度/标准差。根据收集的数据和预先设定的良率规则,即可计算出合格率或良率(即在特定输入条件下,通过合格次数与检验总次数的比率)。 用户还可以根据生成的测量结果与失效规则做对比,对失效进行自定义分类。

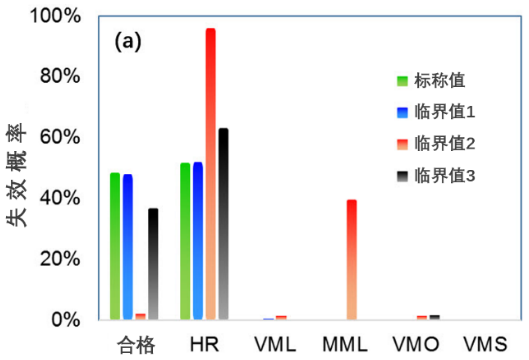

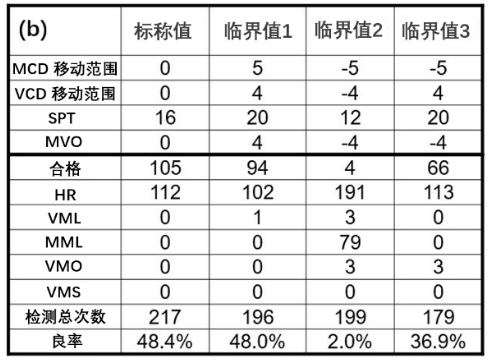

我们首先确定了MCD(心轴CD)、VCD(通孔CD)、SPT(侧墙厚度)和MVO(轴心-VCX轴方向套准精度)的均值移动范围及其分布宽度,之后执行实验设计,用蒙特卡洛模拟方法执行3000次虚拟实验测试。图3(a, b)为四种不同输入条件下的失效类别汇总条形图和良率汇总表,通过这些图表可以看出特定输入条件下发生各种失效的概率大小并由此判断出各类失效模式对良率的影响。

图3. 特定MCD/ VCD/ MVO条件下的良率情况。(a)失效模式条形图,(b)良率汇总

D. 工艺窗口优化

在工艺开发过程中,开展上述分析可能会引发一系列其他问题,例如预测所得的良率是否合理?是否可通过调整规格均值获得更高的良率?放宽工艺分布宽度要求的同时能否保持良率?如果无法达到满意的良率结果,是否可以通过收紧分布宽度以达到目标良率,以及收紧程度如何?要回答上述问题就要用到SEMulator3D中的工艺窗口优化(PWO)功能。该功能可以自动搜索具有固定分布宽度的均值组合,然后再根据所收集的数据得出最高良率(合格率)的最佳工艺窗口。

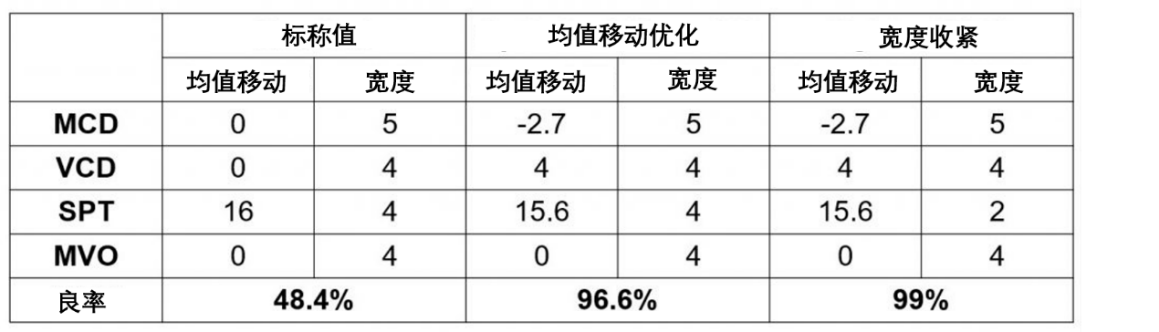

表1 所示为工艺参数优化前,优化后,优化后+收紧SPT厚度条件下的良率及其对应的工艺窗口。通过该表可以看出,只需优化工艺规格均值即可将良率从48.4%提高至96.6%,接下来只需进一步收紧SPT分布宽度值即可获得99%的目标良率。

表1.不同输入条件下的良率汇总表

结论

本文探讨了如何通过虚拟制造提高良率。文中实例采用了因边缘定位误差导致VC-M1良率损失的7nm 6T SRAM模型,采用的技术包括结构构建、模型校准、虚拟量测、失效分类、良率预测和工艺窗口优化。分析结果表明通过工艺窗口优化功能和收紧规格要求可以将良率从48.4%提高到99.0%。可以看出,虚拟制造可广泛应用于各种良率提升研究,而这些研究的结果将推动半导体工艺和技术的发展。

评论