基于PGL22G的物联网Sensor HUB设计

作者 黄国伟(福州大学,福建 福州 350108)

本文引用地址:https://www.eepw.com.cn/article/201901/397270.htm摘要:基于紫光同创PGL22G型号FPGA芯片,进行OpenMIPS软核的移植,使之成为MCU,在软核中通过Wishbone总线进行互联。随后,基于OpenMIPS架构进行μC/OS系统的移植,在μC/OS系统下通过GPIO口进行数据采集,并将采集到的存储至EEPROM中,可通过电脑查询EEPROM存储的数据。通过相应的通信模块进行传感器数据的发送。发送的数据可以在相应微信公众号中实时查看。

关键词:FPGA;OpenMIPS软核;UC/OS II;移植

1 框架描述

1.1 MCU框架描述

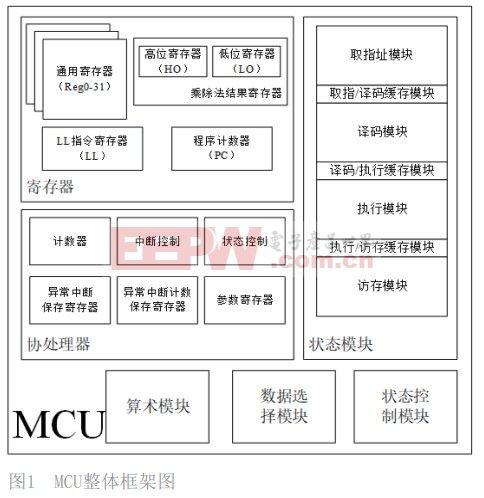

OpenMIPS软核的MCU整体框架如图1所示,MCU主要由寄存器单元,协处理器单元,FSM单元,算术单元,数据单元构成[1]。寄存器单元包括针对32位指令格式的通用寄存器,针对乘除法运算结果的乘除法结果寄存器,程序计数器,存放OpenMIPS相关操作指令的指令寄存器。用于数据处理的算数模块(包括四则运算和部分特殊的数据移位操作),数据选择模块;针对于五级流水线设计的状态模块,其构成与实现于下一段介绍;针对本设计使用的五级流水线还添加了协处理器模块用于工作状态的配置。

1.2 流水线框架描述

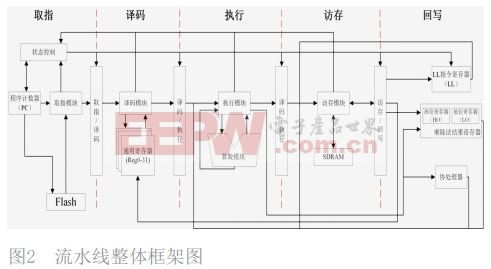

本设计的五级流水线框架如图2所示,结合图1的MCU架构图可见:首先通过取址模块去获取相应指令,与此同时程序计数器技术同状态控制模块数据交互后实现对于当前执行状态的控制,通过译码模块和32个通用寄存器的数据读写实现指令的译码,将译码后的指令放入执行模块进行判断后进入相应的算数模块实现相应的数据计算处理,通过放存模块确定存入对应的寄存器地址,最终将结果放入对应的寄存器[2]。

2 SOPC实现原理

通过PGL22G构成MCU主体,搭载Wishbone总线实现与UART、Flash、GPIO等外部设备的数据交互。

2.1 五级流水线的实现

如图2所示,五级流水线可以概括为取指、译码、执行、访存、回写,下面分别介绍五级各自实现原理。

取指阶段是取出指令存储器中的指令,同时程序计数器(以下简称PC)值递增。PC中,因为一条指令是32位,而设计基于OpenMIPS的MCU是采用字节寻址的方式,由此每条指令对应4个字节,PC每次寻址结束后地址加4。在取指译码模块间有取指译码模块用于缓存取指阶段的指令及其对应地址。

译码阶段是指针对指令给出相应运算和操作的对应操作数,通过32位通用寄存器实现对指令的同时读取和写入。译码模块通过对通用寄存器的访问实现指令对应运算和操作的译码过程,将获取到的指令译出对应的源操作数送出。在译码和执行模块间有译码执行模块用于缓存译码阶段给出的运算类型,源操作数和对应访问寄存器的地址相关数据。

执行阶段是对获取到的源操作数进行相应的指定运算,并将运算出的结果送入到运算访存模块进行缓存。

访存阶段将执行阶段的结果送入回写阶段。

回写阶段将相应的指令与那算结果写入对应地址的寄存器,由此完成一个周期五级流水线的操作。

2.2 指令存储的实现

将FPGA设计为SOPC的初衷便是使用对应MCU指令集的编程方式减少对于设计人员的数字电路实现要求,指令存储决定MCU对应运行指令的正确。结合对于FPGA资源的考虑以及对应MCU指令程序编译烧写的便捷,使用外接SPI Flash作为ROM使之成为指令的存储设备。

首先输入对应Flash工作模式数据,然后通过计数器进行计数实现地址数据的发送,当计数器停止即地址数据发送结束,此时DQ1管脚输出所需数据,SPI Flash读取数据仿真波形如图3所示。

2.3 数据存储器RAM的实现

通过pango软件生成一个地址位宽为14的32位存储器,写操作时根据sel的值修改其中对应的字节即可。由于系统中地址位宽为32,但针对数据存储时所需要的地址宽为14,再结合指令加一即为移动四位因此取系统地址位宽的第2~15位作为存储器对应地址[3]。

2.4 协处理器的实现

协处理器用于系统控制,主要用于配置CPU工作状态,实现高速缓存控制,异常处理和控制,存储管理单元控制。首先对协处理器中的寄存器进行写操作,依次写入地址,将不同的数据保存到不同的寄存器中;依据读取地址,将相应的寄存器值输出即可。协处理器的访问指令只需遵循MIPS32指令集中的访问指令mtc0,mfc0即可。在译码阶段依据指令读出通用寄存器的值,在执行阶段确定写入通用寄存器的值,将信息传递至访存阶段。访存信息传递至回写阶段,回写阶段修改对应地址的寄存器值即可。

2.5 Wishbone总线的实现

Wishbone总线有多种连接方式:点对点、数据流、共享总线、交叉互联等。在点对点连接方式中,有一个主设备和一个从设备。

通过状态机来实现Wishbone的操作和控制。复位的时候进入空闲状态WB_IDLE。当处于空闲状态WB_IDLE时,如果处理器发出了访问请求,且当前没有处于流水线清除过程中,那么会进入总线忙状态WB_BUSY,开始访问总线。但是,如果处于流水线清除过程中,那么本次的总线访问当然会无效,所以不必进入WB_BUSY状态。当处于总线忙状态WB_BUSY时,如果收到Wishbone总线的响应,表示本次访问结束,此时需要判断流水线是否处于暂停状态。如果没有处于暂停状态,那么将访问到的数据送入处理器,进入空闲状态WB_IDLE,等待下一次访问请求。如果处于暂停状态,那么将访问到的数据暂时保存起来,同时进入等待暂停结束状态WB_WAIT_FOR_STALL。当流水线暂停结束时,再将访问到的数据送入处理器,并且进入空闲状态WB_IDLE,等待下一次访问请求。当处于总线忙状态WB_BUSY时,如果发生异常,那么会清除流水线,此时将直接取消此次Wishbone总线访问,并且回到状态WB_IDLE。

2.6 UART和GPIO的实现

UART将并行的数据转变为串行的数据发送,或将接收到的串行数据转变为并行数据。通过串口可以实现与计算机或其他设备的通信。在PGL22G开发板上有串口转USB模块,UART模块控制是OpenCores站点提供的UART IP Core,其兼容常见UART设备;支持Wishbone数据规范。

GPIO是以位为单位进行数字输入输出的I/O接口,作为单纯通用输入/输出I/O,输入时从外部读取输入信号,输出时将写入的值输出到外部。处理器通过GPIO与其他外设相连。GPIO控制是OpenCores站点提供的GPIO IP Core,其I/O口数量从1到32可配置;所有I/O口可以配置为双向接口;输入接口可以触发中断;支持Wishbone数据规范。

3 μC/OS系统的移植

借鉴μC/OS-II在其他MIPS架构处理器上移植的代码进行修改,在Linux中下载版本号为V2.91的μC/OS-II源码以及针对MIPS M14K的μC/OS-II移植代码[4]。去掉includes目录下无需使用的cpu.h文件。os_cpu.h中的文件定义了处理器相关的常量、宏、结构体,这里可以完全使用MIPS M14K的移植代码,无需修改。os_cpu_a.S文件异常处理样例,和一些入堆栈使用的常数,以及一些函数。将OS_CPU_SR_Save中的Status寄存器的最低位修改为0;DisableInterruptSource中的函数对应的Status寄存器中IM字段指定为修改为0。修改os_cpu_c.c文件,将新任务的入口地址task存放到堆栈中对应证书寄存器$31的位置[5];将BSP_Interrupt_Handler函数中的Compare寄存器的值增加0x50000,因为本次系统的频率为27 MHz,为保证中断是在12 ms个时钟周期内发生。将修改后的文件进行编译,最终得到相应的.bin文件,与BootLoader.bin合并后得到相应的.bin文件,将.bin文件烧入SPI Flash中,当OpenMIPS运行时会首先运行BootLoader,后者将μC/OS-II的代码复制到RAM中,然后跳转到RAM,最终控制权交由μC/OS-II,由此实现了μC/OS系统的移植和运行。

4 结论

本设计基于紫光PGL22G FPGA开发板实现了OpenMIPS内核的MCU移植,实现了操作系统μC/OS-II的移植使之构成SOPC系统增加系统的灵活性和稳定性。实现了传感器的数据采集(常见的数字信号和模拟信号的传感器均可拓展实现数据采集,由此实现Sensor HUB),以及数据的本地存储和访问。通过通信数据实现了数据的上传发送,同时可以在微信公众号中进行数据的查询。

在本设计中还有一些可以改进的地方:首先,OpenMIPS架构具有一定的缺陷,我们可将本设计的架构改为RISC-V架构。该架构开源,可以拿到全部的源代码进行裁剪或修改以实现我们的需求。此外,该架构以运算为核心,在大数据上和人工智能上具有无可比拟的优势。其次,在存储上可用DDR存储器来替代EEPROM,因为DDR存储器具有速度快、存储量大等等的优势。最后,可接入更多种类不同的传感器,真正实现sensor HUB的主题。

参考文献

[1]蔡启先,刘明,余祖峰.MIPS64指令集模拟器的建模与实现方法[J].计算机工程,2010,(18):245-246.

[2]刘秋菊,张光照,王仲英.基于MIPS指令集的流水线CPU设计与实现[J].实验室研究与探索,2017,(8):148-152.

[3]雷思磊. 自己动手写CPU[M].电子工业出版社,2014.

[4]陶锐,李洋,曹海燕.基于ARM7内核的UCOS-Ⅱ移植研究[J].企业技术开发,2012,31(05):68+74.

[5]李备,彭楚武,谭凌峰,陈敬恩.UCOS移植中的硬件抽象层构建技术[J].电子产品世界,2006(16):93-94+92.

作者简介:

黄国伟(1994-),男,研究生,主要从事嵌入式系统的研究。

本文来源于科技期刊《电子产品世界》2019年第2期第45页,欢迎您写论文时引用,并注明出处

评论