众厂商谈边缘AI的技术与产品策略

作者 / 王莹 毛烁 《电子产品世界》记者

本文引用地址:https://www.eepw.com.cn/article/201811/395028.htm摘要:人工智能和物联网两股浪潮同时涌现,两者相互融合,相辅相成,不仅推动着技术的发展,也推动着时代的进步。各大元器件厂商对于这两股时代浪潮也各有高见。

实时低功耗AI处理解决方案

瑞萨电子致力于为实现环保,智能型社会而贡献力量,而仅通过使用云的大数据处理是无法实现更安全和健康的生活的。

凭借灵活且可扩展的嵌入式人工智能(e-AI)概念,瑞萨电子提供了面向未来的实时低功耗AI处理解决方案,该解决方案在业界是独特的,它可在嵌入式端点设备中实现人工智能的特定需求。瑞萨正在为其智能工厂、智能家居,智能基础设施和新业务部门方向努力,例如服务机器人等重点领域的客户探索新的嵌入式人工智能解决方案。 瑞萨电子将继续与客户和合作伙伴展开合作。

通过使用由UC

Berkeley开发的Caffe或Google开发的TensorFlow,任何人都可以相对轻松地使用AI(人工智能)。DNN(深度神经网络)是在各种AI专业领域中最常用的算法之一。DNN由两个主要部分组成:

学习和推理。

DNN在学习和推理执行所需的计算量方面存在很大差异,它的一个主要特征是它在推理阶段可以以较低的计算能力执行。

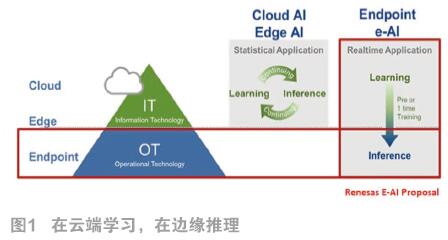

瑞萨电子的e-AI解决方案提议是在Cloud方面继续学习执行,但推理执行转移到MCU / MPU(如图1)。 优点是它可以支持更安全,可靠,快速的AI系统。

为了在嵌入点中执行推理阶段,嵌入式AI 方案有两个主要挑战:

1.嵌入式系统实现AI的难点在于,AI系统和MCU / MPU的语言不同。 将AI模型转换到MCU / MPU并不容易。 我们需要有一个有效的工具来转换模型,然后妥善适合MCU / MPU存储区。

(备注:Python是在许多AI模型中比较通用的语言,而MCU的控制程序通常用C / C ++。)

2.AI推理将迁移到边缘和端点系统,作为新的硬件架构解决方案, 它必须真正平衡行业领域的要求,包括解决功率效率、市场灵活性、功能安全要求和实时响应。瑞萨电子有相关的技术和开发环境来解决这两个问题。

支持e-AI开发环境

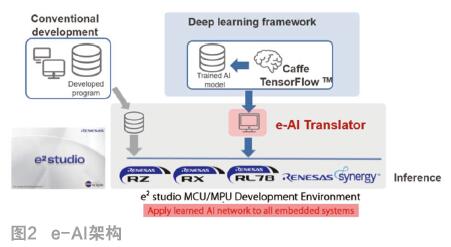

瑞萨电子e-AI人工智能开发环境可以把学习后的AI模型输入到e-AI翻译器,并将其转换为e²Studio C / C ++项目的可用形式。它是一种方便易用的工具,把AI功能简单地实现到MCU / MPU上(如图2)。

DRP技术实现低功耗AI处理

动态可重配置处理器(DRP)是一种可编程架构,可动态切换数据路径,使高度复杂的加速器能够在不增加功率要求的情况下运行并行指令。FPGA和DRP在逻辑中使用类似的布线结构和并行技术,但DRP由大型子组件组成,而不是像FPGA那样的细粒度配置。这意味着DRP重新配置所需的时间比包括FPGA在内的其他架构要少。

DRP的可配置性允许架构继续适应和支持深度学习神经网络的变化。DRP技术具有高速处理能力和消耗更少功率的特点在嵌入式AI系统拥有明显优势。

面向轻型机器学习,恩智浦出台eIQ开发环境及芯片

机器学习将驱动下一波MCU增长

IoT推动了这几年MCU的更新换代,而下一波MCU的助推器是终端的机器学习,包括家庭环境、声音处理、手势控制、智能感测、智能控制、多摄像头观察、个人资产、主动目标识别、AR(增强现实)等。

典型的案例之一是目前发展火热的人机界面的声音处理,会推动下一波白电等家电应用的需求。例如在2018年10月的Arm TechCon2018(Arm技术大会)上,恩智浦展示了声控洗衣机,可以与洗衣机对话,例如:“打开洗衣机”。洗衣机会问:“你要怎样洗?”可以回答:“我要标准洗”或“强力洗”。也可以告诉洗衣机洗什么样的衣物,例如洗被子,或用什么方式洗,例如热水洗、冷水洗等,洗衣机就自动设置好。

再例如图形的识别,恩智浦在美国的一个DEMO(演示)是交通指示标识识别,机器能够识别红绿灯、是路还是人,假设指示标识斜着、模糊一点,机器都可以辨认出来。

边缘AI的芯片布局

恩智浦有全套的MCU、MPU产品线,从低端MCU一直到高端的四核、八核高端处理器,所有这些芯片都可以用在机器学习、边缘计算上。客户不仅可以在云端进行训练,还可以通过软件的推理,在终端的处理器上进行应用。

恩智浦的AI开发环境是eIQ,也是机器学习(ML)的开发环境。底端的硬件平台有传统的MCU和MPU,诸如Kinetis、LPC等Cortex-M核的MCU产品,还有新的i.MX RT系列跨界处理器,高端的i.MX6、7、8等处理器,以及Layerscape处理器。

硬件平台里,运算的部分是核和硬件加速器,有Cortex-R、M和A核,GPU、DSP中放的是DSP核,未来一两年内,恩智浦还将开发ML(机器学习)的加速硬件,这不同于大型的云端硬件加速,而是可以跨平台、跨处理器和微控制器的用于终端计算的ML加速器。

在芯片之上是硬件抽象层,诸如OpenCL,OpenVX,Arm的计算库/ CMSIS-NN,还有恩智浦的API等。再往上是推理机(Inference Engine),有很多种,主推的有Google的TensorFlow、TF Lite等。实际上,恩智浦支持所有开发环境。现在还有新的NN Compiler(编译器),例如Facebook的GLOW等。

在基于所有的机器学习软件硬件结合之后,恩智浦推出了全套的解决方案,包括音视频及机械传感器的解决方案(例如压力、加速度传感器的解决方案)。同时针对各种应用,推出了应用上的解决方案,例如ISP(图像信号处理)、图像加速、传感器融合、全景环视(注:过去通常是车上用,现在家居方面也有很多应用),还有前端的声音的控制,诸如多扬声器。

在扬声器方面,如果是两个扬声器,用比较简单便宜的MCU就足够了,例如LPC和Kinetis系列;如果更多扬声器,由于数据处理量很大,适合用i.MX RT跨界处理器平台,或i.MX 7、8、8M等高端处理器。

可见根据不同的应用,恩智浦有不同的处理器配合,这是eIQ的概念。恩智浦的目标是让外界主流的推理机都能运行在恩智浦的硬件上。

恩智浦也有全套的芯片,覆盖高端到低端。其中高端的i.MX用的是GPU、DSP,未来一两年内,恩智浦还会推出ML加速硬件,是真正的专用加速器。

赛普拉斯:物联网产品的高性能软硬件解决方案

随着越来越多的物联网设备接入和应用的复杂多样化,边缘计算和安全越来越多地被市场讨论且成为关注焦点。这些新的技术和趋势对嵌入式芯片是机遇也是挑战。

物联网的部署是为了更智能、更便捷和更有效率,因此人工智能的应用是一种必然的趋势:通过真实世界量化后的大数据分析,由计算结果代替或者辅助执行使得结果更优化。这些分析和计算通常在云端进行,然后随着对实时性的要求提升以及应用场景的复杂程度,越来越多的应用开始考虑把计算放在物联网终端或者节点端,比如智能语音识别的本地化,比如3D人脸识别的图像预处理本地化等。这样的应用要求处理器具有高性能的处理能力,同时满足低功耗、低成本的物联网设备的普遍需求,整体上提升了嵌入式芯片的处理能力和性能功耗比的门槛。

与此同时,物联网安全也开始从可选项变为必选项,随着愈加成熟和详细的行业规范的推出,比如智能门锁,物联网设备对安全的需求从简单的数据通信加密、安全启动防篡改,发展到需要有效和安全的硬件隔离来实现可信执行环境,从而确保物联网的安全服务,不受其它应用服务的更新的影响或者非安全访问的威胁。这对嵌入式芯片的安全架构提出了更严格的要求。

赛普拉斯半导体的PSoC 6微控制器结合了以上提到的高性能、超低功耗和高安全性特点,从系统架构和工艺上一开始就考虑了边缘计算和高安全的物联网需求,是为下一代物联网量身定制的处理器。同时结合赛普拉斯领先的Wi-Fi和蓝牙无线连接技术,以及结合了PSoC Creator和WICED无线应用SDK(软件开发包)的Modus Toolbox开发工具,为物联网产品开发者提供了完整的高性能软硬件解决方案。该开发套件不仅集成了本地语音处理和身份验证等计算功能,还在PSoC 6双核架构基础上实现了灵活、安全的可信执行环境,并提供亚马逊和阿里巴巴的安全云服务连接开发套件。赛普拉斯公司新成立的物联网计算和无线部门在未来五年将继续大力开发物联网芯片、软件和解决方案,为市场提供好的产品和服务。

面向AI等应用推出自适应加速平台及加速卡

对于几何级变化的数据计算时代,芯片的开发速度已经远远跟不上创新的速度。为此,Xilinx于2018年10月推出了自适应加速平台——ACAP,是软硬件可编程平台,首款产品名为Versal,制程7 nm,包含FPGA和异构加速等复杂结构。为了满足数据中心加速需要,Xilinx还推出了Alveo加速器卡,用于数据中心和AI,芯片制程16 nm。其中,Alveo U200 和 Alveo U250 由 Xilinx UltraScale+ FPGA提供动力。

灵活芯片与专用芯片的应用比拼

那么,既然现有芯片已经很难跟上数据和计算的几何级发展,固定功能的AI芯片发展前景如何?实际上,ACAP或者Alveo产品不会取代所有GPU,但是人们肯定会越来越多采用灵活应变的平台。

相比GPU、CPU,ACAP的引爆点在哪里?GPU现在在深度学习训练这一块应用非常多,但是它的功耗很高。但是Xilinx并不是特别关注训练这个市场,而是更多关注后面的推断这部分的市场,包括在数据中心和边缘计算,GPU用得并不多,CPU有一定的应用,但是性能和时延不太理想。这也是为什么Xilinx在推断这个领域,包括在智慧城市、自动驾驶汽车上已经有了很多的订单,相比GPU、CPU更有竞争力。

反过来再看训练市场,现在GPU占据的市场份额比较多,但是这个市场基本处于饱和的状态。而推断这个市场仍然处于初期、快速上升期,现在正处于从CPU向加速卡转换的阶段,很多分析师预测未来的推断市场比训练市场规模大很多,因为训练只需要一次,但是最终推断可能是成百上千倍的应用规模。

如何看待很多初创公司在做AI芯片?

现在无论是AI还是别的类型芯片,任何的先进技术要发展,如果是用16 nm、7 nm的技术,所需要的投资都是巨大的,很多小企业可能没有足够的资金,无论是在芯片的开发还是在量产方面,尤其实现量产需要非常大的投资,这对于所有做AI和其他应用的企业来说都是一大挑战。

既然如此,AI初创公司应该如何去创新?被大公司收购是出路之一,例如2018年7月,北京的深鉴科技公司被Xilinx收购。因为大公司能够充分利用创新的技能和知识来扩大客户群,帮助小公司更快地影响业界,而无需初创公司自己去融资,还要来重复执行大公司很多优势领域的方案。所以初创企业应该关注自己的创新,而大公司擅长的部分可以由大公司来做,而不是由初创企业投资几亿元去做芯片。

深鉴的技术特色

Xilinx过去几年在AI边缘计算上投入了很多资源,例如2018年7月,Xilinx收购了深鉴科技。深鉴科技也是用赛灵思的 Zynq SoC技术,面部识别就是深鉴非常重要的一个技术应用领域。深鉴科技有一个剪枝技术,是基于神经网络来进行优化的技术,也就是将神经元需要计算的数量来进行裁减,使得真正计算的神经元少一些,即使一些小的FPGA也可以进行计算。

类比一下,就像一个小孩小的时候脑神经元比较多,长大的时候使用的神经元数量反而少了,但是这些神经元的可用效率和效果是非常好的,随着人逐渐长大,对神经元的训练使得少部分的神经元更加强大了。还有模块上的系统FPGA可以嵌在IP摄像头和PCI-e卡里,这都是在边缘计算里的。

高精度的FPGA架构

无论是作为协处理器、独立的处理单元亦或是简单的桥接,只要客户寻求的价值定位是创新、快速上市、低延迟、灵活的IO以及可编程性,FPGA就有其独特的优势。灵活IO可以在不同的应用场景支持不同类别的传感器,甚至处理多个传感器交互和融合。AI目前还在初步阶段,莱迪思预计神经网络引擎需要可编程性持续演进和优化。通用的MCU功耗和延迟一般会较高,加入固化的加速器虽然可以改善当下的性能,在未来几年内不能持续优化的缺陷会是个很大的限制。在新一版的CNN加速器IP,莱迪思针对了神经网络的需求来优化了DRAM存储器带宽,使得ECP5的推理性能最多提升至2倍。

随着AI不断火热,IoT和智能传感器市场将持续增长。物联网世界的多样性也将是FPGA灵活架构大放异彩的机会。因此在超低功耗、低成本、小尺寸的iCE40 UltraPlus上,莱迪思也推出了轻量化CNN来满足更灵活的性能、精度、功耗的平衡与取舍。尽管轻量化CNN比之前推出的二值神经网络(BNN)功耗稍高,但是其精度和性能也更优秀,CNN在业界的接受度也比BNN更为广泛。

更高性能的边缘应用

Achronix的FPGA产品和技术专注于边缘应用上的多种人工智能(AI)需求,例如汽车传感器融合、目标检测和识别、AI和机器学习,以及360度环绕视图系统等需要在边缘上本地处理数据的应用。

可编程逻辑提供了使计算更加以数据为中心的能力。虽然传统的处理器都要求数据通过复杂的高速缓存层级被送到其流水线中,而可编程逻辑则能够构建数据流水线。借助由定制逻辑电路和数字信号处理器(DSP)引擎组成的数据单元来在数据通过时操控它们,数据可以从一个节点到另一个节点无缝流动;每个单元都已准备好把数据转发到需要它们的下一个节点。随着需求的变化,其中的逻辑阵列可以轻松地重新连线形成新的配置。与更适合处理控制密集型代码的微处理器相比,这种逻辑阵列可以为以数据为中心的应用提供更好的支持。然而,独立FPGA芯片通常会产生更大的功耗,这是因为需要将数据频繁地移入和移出更专用的ASIC芯片中。

嵌入式FPGA(eFPGA)技术提供了一种方法,可以在一个封装芯片中满足边缘计算应用的能效、性能、延迟和面积限制。结合eFPGA技术,可以把平时部署在独立的ASIC芯片中的常用功能在定制硬件中实现集成,以带来更高的性能和密度。对于机器学习应用,这些功能可以是用于卷积内核或最大池计算的专用处理器阵列。通过在同一芯片上集成可编程逻辑和定制逻辑,可以避免在芯片外传输数据,从而节省大量功耗。

有关开发环境和技术方面内容如下:

Speedcore™嵌入式FPGA:它是经流片验证的高密度、高性能eFPGA半导体知识产权(IP)产品。

Speedchip™ FPGA合封芯片:FPGA合封芯片专为嵌入到先进的系统级封装(SiP)解决方案进行了优化,如通过硅介电层或有机基板实现了2.5D封装。

Speedster®22i FPGA:这是一系列高性能和高密度FPGA芯片,带有适用于通信应用的嵌入式系统IP,包括10 G / 100 G以太网、100 G Interlaken、PCIe Gen3×8和DDR3等。

PCIe Accelerator-6D加速板:它们是具有业界最高存储器带宽的、基于FPGA的PCIe附加卡,适用于高速加速应用。

Achronix®的自动化设计(CAD)环境被称为ACE,它与行业标准的逻辑综合工具配合使用,使FPGA设计人员能够轻松地将其设计映射到Achronix FPGA芯片中。

支持生态系统与AI的开发和应用

Imagination的业务是为半导体芯片提供必要的内核构建模块。Imagination主要以自己的嵌入式图形(GPU)技术和神经网络加速器(NNA)技术而闻名,并将这些技术授权给全球领先的芯片供应商。他们的半导体芯片广泛应用于多种产品和服务,因此Imagination在市场中拥有非常独特的地位,因为Imagination可以支持整个生态系统参与人工智能(AI)的开发和应用。

GPU和NNA现在是边缘AI的必要元素。随着众多企业开始认识到在各种任务(从自然语言处理到图像分类)中应用神经网络的潜力,引入人工智能元素的产品数量也开始稳步增加。同时,这些任务的处理正在从传统的基于云架构转移向设备端本身,基于硬件的专用神经网络加速器现在可嵌入至半导体芯片中,以实现本地的AI处理。从可监控前方道路的先进驾驶辅助系统(ADAS)到虚拟助手等声控的消费性电子产品,关于集成的、基于神经网络AI的机会正在向多个细分市场延伸。

不可否认,AI正在成为许多应用的必要元素。但是,仍然有很多挑战。其中之一就是在边缘和云之间平衡处理负载,并找到放置AI本身的最佳位置。例如,边缘AI可用于消费性设备上的本地语音识别,比如识别“唤醒词”或简单指令,但是依然有必要在云端进行大部分的语音AI处理,以便利用那些无法在设备端存储的庞大知识库。现在许多设备都标榜带有AI,但实际上,除了依靠云端去给人智能的印象以外,就仅仅只是在本地做了简单的模式匹配和识别而已。

半导体工艺不断演进,为在边缘设备上进行更多的AI处理创造了机会。例如,Imagination将看到能够监控特定事件的智能安全摄像头。它们将使用边缘AI处理来识别视频流中的特征,例如道路上的车辆或镜头中的人脸,然后触发特定事件,例如计算车辆的数量或允许授权人员访问。他们甚至可以通过减少“误报”的数量来节省成本,因为摄像头中的边缘AI可以识别正常行为和可疑行为之间的差异。

另一个挑战是,尽管AI应用的数量在不断增加,但这并不一定意味着集成了AI加速功能的SoC是所有应用场景的前进方向。的确,如果Imagination考虑AI去覆盖大部分细分市场,那么由于使用该技术的各种产品具有截然不同的工艺要求,碎片化会自然而然地发生。碎片化的市场对于使用专用SoC提供服务具有挑战性,所以“一应俱全”的方法不会始终适用。虽然诸如手机或ADAS(高级驾驶员辅助系统)等一些市场为SoC供应商提供了大量机会,但许多以人工智能应用为目标的市场将自然呈现出低销量前景。例如,一些产品可能需要AI进行语音处理或图像识别,但不是两者都需要;同样,智能家居供应商不大可能只为将AI功能嵌入他们的控制面板而去使用原本为智能手机设计的SoC,因为这不符合成本效益。这个难题的解决方案就是打造专用的AI芯片,其可以作为辅助芯片与主应用处理器一起使用,去卸载通常由主应用处理器中的NNA内核处理的AI推理任务。这样做的优势是SoC供应商可以提供一系列具有不同性能水平的边缘AI芯片;同时,原始设备制造商(OEM)可以根据他们希望在自己的特定应用中所处理的AI处理开销来选择适当地扩展产品解决方案。

RISC-V适合AI、物联网等创新

有人预言,RISC-V或将是继Intel和Arm之后的第三大主流处理器体系。实际上,三年前RISC-V基金会刚刚成立,如今已有200余家会员,会员遍布27个国家,得到了来自中国、印度、俄罗斯等国政府、高校、企业界的支持。RISC-V为何在短时间内受欢迎?

相比Intel和Arm,RISC-V有三大特点。

首先,从微处理器角度看,RISC-V的Core(核)设计得非常精巧、简单、有效,允许运行基本的操作系统。

其次,允许可扩展,由非营利组织——RISC-V基金会运营的,不像过去Intel和Arm等是由一家公司运营的,RISC-V核是大家(Community)运营的,只要加入基金会,成为基金会成员,就可以用。RISC-V的可扩充性允许开发者加自己新的指令,而且允许开发者的设计是开源的,也可以不开源,也可以用来赚钱,也可以做研究……这种灵活的模式带来了微处理器的革命。实际上,RISC-V是第一个硬件开源的,开源了ISA。ISA指令集是硬件与软件的接口。

第三,带来很多创新。在微处理器产品里,从IT和IC领域里,很长时间里被Intel垄断的,之后有Arm。由于知识产权的限制,其他公司不能使用Intel或Arm的ISA指令来做自己事情,除非得到授权。因此,多年来,很少有开发者在架构方面做创新。不过,RISC-V开了一扇门,允许公司、高校师生、研究机构等做产品或进行研究。有个形象的比喻,过去只有一种榔头,做任何事都要用这个榔头,现在允许大家开发各种各样的榔头。

值得指出的是,RISC-V并不是比Intel和Arm好。因为Intel和Arm也是非常优秀的公司,投入了大量资金和努力,开发了很好的产品。区别在于那两种芯片/架构是私人所有的,不是开放、免费的,RISC-V是第一个在微处理器领域里把ISA指令架构开放,这是一场革命,带来了全新的商业形态和创新环境。

原来的商业模式,Intel和Arm把产品做好了,无法改变。但市场上应用场景在变,目前已经超越PC和手机时代了。在很多应用场景,例如AI、物联网和区块链等有很多创新的应用,对架构有新的要求,老是用一套做是不行的,RISC-V允许核本身不动,基本ISA由community(社区)统一管理,允许加不同的东西进来,这样可以把很多事情做好。

RISC-V的ISA是开放和免费的。有三种模式:1.有可能开源社区获得免费的设计,像Linux;2.商业模式方面,有的是像致象尔、SiFive、晶心科技等公司,利用ISA设计芯片,销售IP和设计,出售证书(licensing)或royality(版权);3.卖芯片。由表1可见,Arm不做芯片,只做设计。Intel不卖设计,只出售芯片。RISC-V在这三个方面都可以。

参考文献:

[1] 任泽坤.芯片厂商引领广电的人工智能化[J],电子产品世界,2017(10);19~23

[2] 王莹.人工智能的进展及发展建议[J],电子产品世界,2017(2);19~23

[3] 有鹏,刘勇,杨林莉,等. 基于物联网的图像监控系统[J],电子产品世界,2017(7);37~40

本文来源于《电子产品世界》2018年第12期第11页,欢迎您写论文时引用,并注明出处。

评论