怎么采用FPGA原型系统加速物联网设计?

当我们谈论物联网 (IoT) 的时候,不夸张地说,它可以将我们所使用的智能设备互相连接,彼此分享大量的数据,从而使我们的生活更高效。这不仅仅是消费者对智能家居、娱乐和可穿戴技术的需求,也是工业、军事和政府应用,如智慧城市和工厂等改变了连接局面。

本文引用地址:https://www.eepw.com.cn/article/201808/385495.htm从非常小到巨大

当我们从这个角度来探讨物联网,我们了解到这些设备的范围可以从最小的设计,由少量传感器和驱动器组成的仅几百万门规模的机器,到极其复杂的机器包含几百个传感器和数十亿门的规模。无论规模和复杂度, 这些智能系统都需要大量的软件和真实环境测 试,特别是在整合商业 IP的过程中。所有的物联网案例都提到了连接的可互操作性、复杂的控制和测试效率,这些都 迫使设计团队不得不重新思考其发展策略。再加消费类物联网设备对产品上市时间的压力,很显然工程师需要适当的解 决方案来解决这些问题。

让你在设计初期信心倍增

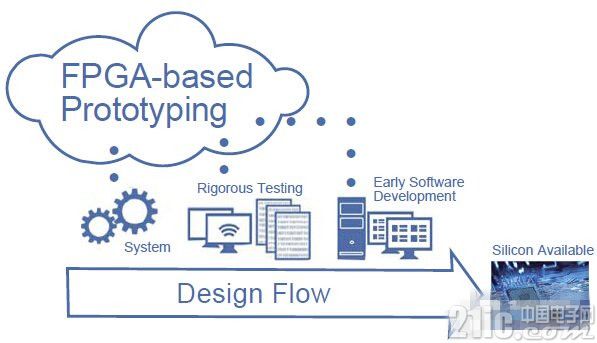

基于FPGA 的原型系统是专门针对物联网设备的设计和验证的复杂性需求。随着原型技术在设计分割以及多 FPGA 联 合调试领域的进步,基于FPGA 的原型系统不仅可以满足百万门级的设计需求,还可以实现设计规模高达15 亿门。基 于FPGA 的原型系统允许设计人员在硅芯片可用之前就可以在一个全功能的硬件平台上先行开发和测试他们的系统级软 件。硬件原型是唯一的可用于早期的实际软件开发和测试的解决方案。软件模型无法提供像硬件平台那样的准确性和可 靠性下的速度和容量。

即使是最小的设计也必须面临非常复杂的软 件问题,需要大量严苛的测试,花费惊人。 这种类型的测试的性质是可以运行,但上市 时间窗可能面临考验。“仿真VS 原型系统 –性能曲线图”这篇文章在FPGA 原型验证 速度和测试好处等方面进行了深入的探讨。 尽管最初设置原型系统可能花费数周时间, 但在初始设置后短时间内进行大量的测试。 以最小速度(5 兆赫)或者四周的初始设置时 间计算,FPGA 原型可以完成数量惊人测 试,这远高于其他解决方案。

事务处理器是物联网设计成功的关键

基于FPGA 的原型系统是非常适合呈现设计从RTL 映射到FPGA。然而,许多物联网设计不可能完全映射到FPGA, 或者可能部分设计仍然只能以C++ 或SystemC 等行为模型描述。在这些情况下,事务级接口能够桥接行为模型和真实 硬件。

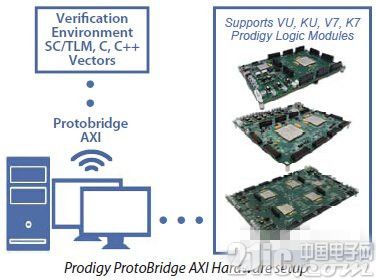

这些事务处理器提供了一种交互方式,使得主机上运行的软件和基于FPGA 的原型系统可以相互通信,通常包括内存、 处理器和高速接口等。S2C 独有的申请专利的 Prodigy ProtoBridge? 系统正是允许这种类型的高速通信一个解决方案。 ProtoBridge 提供软件程序和基于AXI 总线的硬件接口。其中有两个关键部分:连接到PC 主机的AXI 到PCIe 桥接模块,通过桥接模块进行通信的C-API 函数库。该 软件为设计人员创建了基于 ARM 系统提供了新的灵活 性,并且PCIe 接口的传输速度高达1000MB/s,为数据 密集型应用提供了一个完美的开发平台。

这样的系统允许设计人员将FPGA 原型系统的优势最大 化,包括在项目中进行早期算法验证、IP 设计、仿真加 速度和边界测试的验证等等。FPGA 原型系统结合事务 处理器接口可能在整个设计流程中进行一系列的有趣的 应用。

完善的解决方案

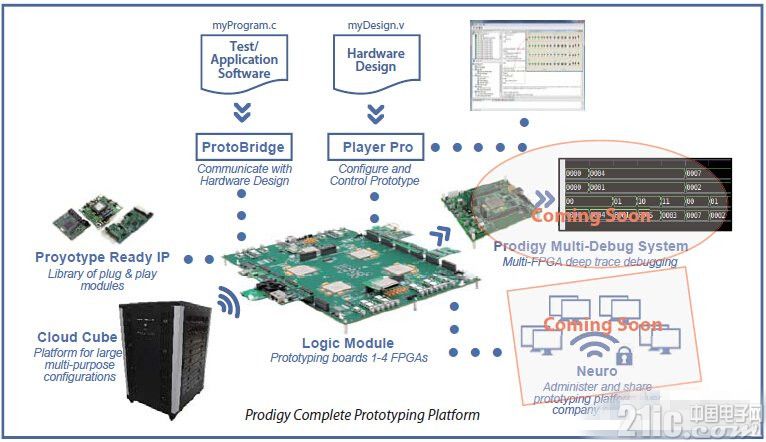

除了 Prodigy ProtoBridge 系统在物联网设计中起重要作用,S2C 的Prodigy 完整原型平台还可以为物联网设计流程的 各个方面提供解决方案。我们提供最全面的原型验证系统以适合您的设计规模,以及最丰富的预测试原型 IP 库和参考设 计流程,加速和简化您的原型验证过程。我们的 Prodigy Player Pro 软件可协助您进行原型配置,并提供远程系统监视 和控制功能。在编译功能在PlayerPro提供了先进的设计分割功能,即将发布的Prodigy MulTI-Debug 模块则可以缓解 多颗FPGA 联合调试的任务。S2C 的 Prodigy FPGA 原型系统解决方案是目前市场上最全面的能帮助您实现物联网设计 的解决方案。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

评论