高压静电除尘器中振打控制电路的EDA设计

0 引言

本文引用地址:https://www.eepw.com.cn/article/201807/384374.htm随着国家对烟气排放要求越来越严格,电除尘器技术已被广泛应用并取得很大进展。振打控制是电除尘器的基本功能之一,是实现“全自动控制”不可或缺的环节。对整个静电除尘器的启动、停止、紧急停机功能一般系统都能做到,但其间程序繁多,且出现问题不易修改,使得无法更好地将振打的理论效果较好体现于实践中。

文中设计了一种新型电除尘器振打控制电路,利用EDA(电子设计自动化)技术,采用先进的VHDL硬件电路描述语言,使得尽管目标系统是硬件,但整个系统的设计和修改如同对软件作用一样方便和高效。

1 电路设计原理

智能型振打控制要求振打及时且不引起二次扬尘。此处设计的振打控制器,可以实现准确控制振打电路的通断,并根据实际需要设置振打间隔周期,以及每次振打的时间等。由现场测量得知,电除尘器的振打要求是:电源接通后,系统先进行一次20S的振打,经过延时一定周期—40min后,再进行20S的振打,周而复始,以保证电除尘器的正常运行。这个环节的主要组成部分是一个脉冲发生器,文章是通过控制脉冲波形,来实现周期的一定性和每次振打时间的准确性。

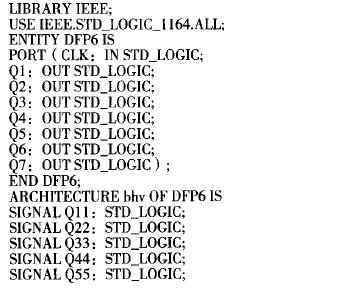

2 20S的延时振打电路

对于20S延时振打电路,是通过由CC555构成的单稳态电路来实现。单稳态触发器只有一个稳定状态和一个暂稳态,在外界触发脉冲的作用下,电路从稳态翻转到暂态,然后在暂态停留一段时间Tw后又返回到稳态。此处暂态控制20S的延时振打。延时振打时间Tw只与元件R和C的参数有关。要使Tw=20s,只需令C=lOOuF,R=200k。电路如1所示。

图1 20S的延时振打原理图

3 40min周期控制的电路

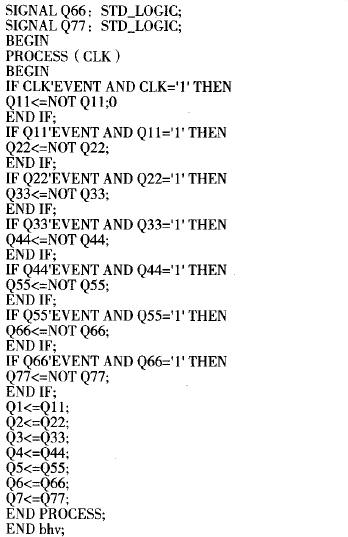

对于20S周期的系统,要将其转化为40min,采用由七个D触发器构成的二分频计数器来实现,二分频的结果是频率降低一半,周期增加一倍,即初始周期为20S,经过7个二分频器后,其周期依次变为40S、80S、160S、320S、640S、1280S、2560S。

第1个D触发器的输入时钟为需要分频的系统时钟,将该D触发器的输出取反做该触发器的输入;第2个触发器的时钟为第1个D触发器的输出,将第2个D触发器输出取反作其输入,依此类推。

40min周期控制的VHDL代码及仿真波形

电路七次分频(即1280S变2560S)的VHDL代码:

仿真波形如2所示。

图2 七次分频仿真波形

4 结束语

通过7个连续的D触发器和555单稳态触发器分别实现40min的振打周期和20s的延时振打。此设计可以严格控制,调节振打时间。对于不同性质的粉尘,可通过修改VHDL程序及参数设置对所设电路的调整,实现针对性振打。经过QuatusⅡ仿真,所示各项指标均符合设计要求,从而验证了该设计方案的正确性与可行性。

评论