嵌入式FPGA IP助力5G芯片快速上市

作者 Mike Fitton

本文引用地址:https://www.eepw.com.cn/article/201807/382661.htm展望未来十年,5G的发展将会使无线基础设施将会变得更加无所不在,甚至还将与我们生活的方方面面更紧密地结合在一起。5G在继续推进以前的蜂窝移动标准持续推动带宽扩展这种范式的基础上,还将推动一系列新的设备和应用模式的产生。

尽管前景让人兴奋不已,但是5G对吞吐量、可靠性、普及性和边缘计算的要求,正在为现有的通信基础设备带来巨大的、新的挑战包括:

1)对低延迟和更高数据吞吐量不断增加的需求,使这些解决方案为了高效处理数据而转向一种更加优化的数据流水线,例如传输时间间隔(TTI)这一重要的时间单位将从1 ms缩短到0.2 ms。

2)应用模式和需求的不断增加意味着不可能再是“一种模式打天下”,这将需要一种基于产品或技术组合的模式,也就是说需要在不同的部署模式间尽可能地实现设计重用的最大化,如从小基站到宏基站,再到Cloud RAN。

3)特别需要的是用灵活性来满足新的和未来出现的应用模式,更直白地说就是大家都期望这些解决方案应该做到面向未来不过时,可以适应来自最终客户和运营商的新的和未预见到的需求。更进一步地说明就是:这种能够可编程的、面向未来的解决方案可以支持改善上市时间。因而在ASIC或SoC流片之前不再必须完全固定设计,在规范最终确定时可能产生的变化将由可编程硬件的方式来应对。

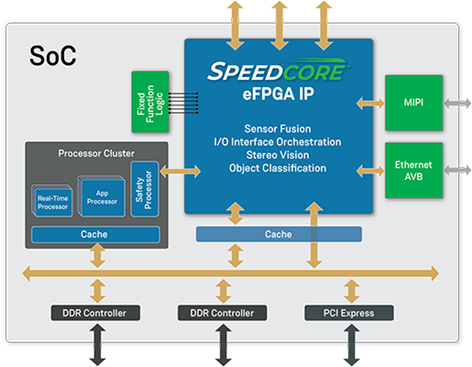

Achronix高度可编程的嵌入式FPGA解决方案

诸如Achornix的Speedcore™ eFPGA(嵌入式FPGA)这类高度可编程的嵌入式FPGA解决方案可为5G系统带来更快的上市时间。例如,没有必要把一款SoC的流片推迟到5G标准最终确立之后,后期发生的需求变化可以用软件或者可编程硬件来解决。这是一种非常强大的优势,可以用来面对5G早期部署中持续的、甚至不断增加的压力,以及一直不断会发生的新标准融合。

评论