AI架构创新和高端芯片发展

作者 / 魏少军 清华大学微纳电子学系主任 (北京 100084)

本文引用地址:https://www.eepw.com.cn/article/201802/376161.htm魏少军,博士,教授,清华大学微纳电子学系主任,清华大学微电子学研究所所长,清华大学移动计算研究中心主任 。

摘要:在“2017中国集成电路产业促进大会”上,清华大学魏少军教授就架构创新和高端芯片发展做了相关报告。根据魏少军教授会上报告整理,已获作者授权。

0 引言

随着近年来人工智能(AI)的兴起,AI芯片的需求量越来越大,性能要求越来越高。而AI运算量很大,这就意味着其需要有足够高的运算速度,预计其运算速度需要达到每秒几千亿次。如果从能量效率角度分析,大概要做到每瓦1万亿次。因此,国内做AI芯片的企业大部分还在用专用芯片在做。采用专用集成电路的问题在于,当网络一旦变化,专用集成电路做成的芯片将无法应对再应用。这就为可编程器件带来了机遇。

1 FPGA难以达到AI的要求

可编程器件的一个优点是可以通过软件的方式来改变芯片的功能,从而适应各种不同功能的应用。最终提升销量,从而分摊产品的成本。

而现在较为常用的可编程器件——FPGA仍然存在诸多问题,还难以达到AI的速率及通过软件改变芯片功能的需求。

1)FPGA的配置信息量很大,多达数十兆字节,因而所需配置时间也很长,大概要几十毫秒,甚至几秒。

2)能量效率低。FPGA面板利用率很低,大概只有5%用来进行计算,95%用来配置信息。正因为其95%是用来配置用的,还要耗电,因而能量效率很低。

3)另外,由于各方面原因,FPGA往往需要最先进的工艺,同时还必须要有电路设计的支持,这也带来了高设计成本。

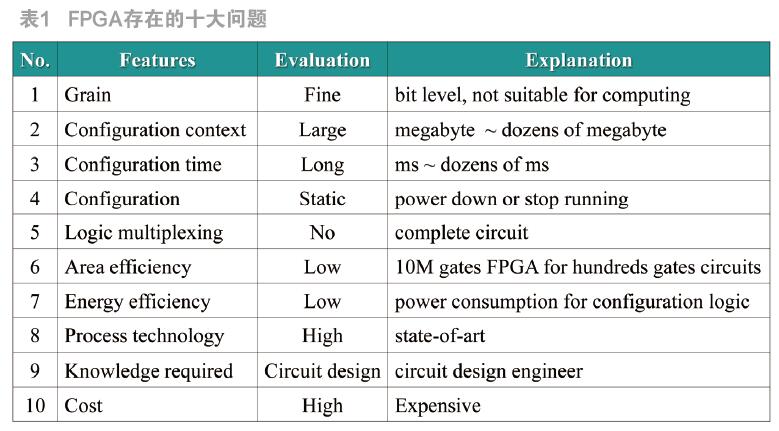

FPGA存在的问题总结起来包含十点:高细密度、配置信息量大、配置时间长、需要断电静态配置、没有逻辑复用能力、面积利用率低、能量效率低、工艺要求较高、对开发人员知识储备要求高、价格贵,具体如表1所示。

2 理想的硬件结构

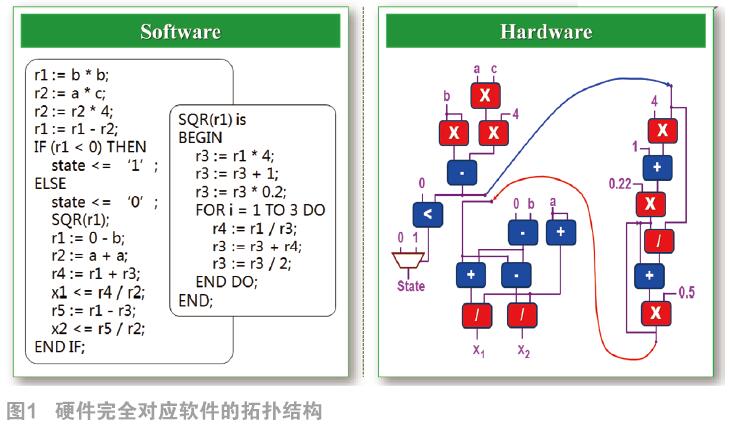

如图1所示系统架构为设想的理想系统架构。其中左边为软件(应用),如果不考虑硬件的代价,左边有怎样的操作,右边就要对应怎样的硬件,左边和右边的拓扑结构是完全一致的。从计算上来看,这样的结构一定是效率最高的。

在这样的架构中,软件可以无穷大,例如写一个循环语句,可以一直循环下去,但是硬件不论多大都是有边界的,这就需要将软件分块搬到硬件上按顺序执行。这样搬的过程中,右边的硬件架构其实是在不断变化的,我们称之为架构和功能可以动态按照软件要求实时改变。

3 软件执行方式

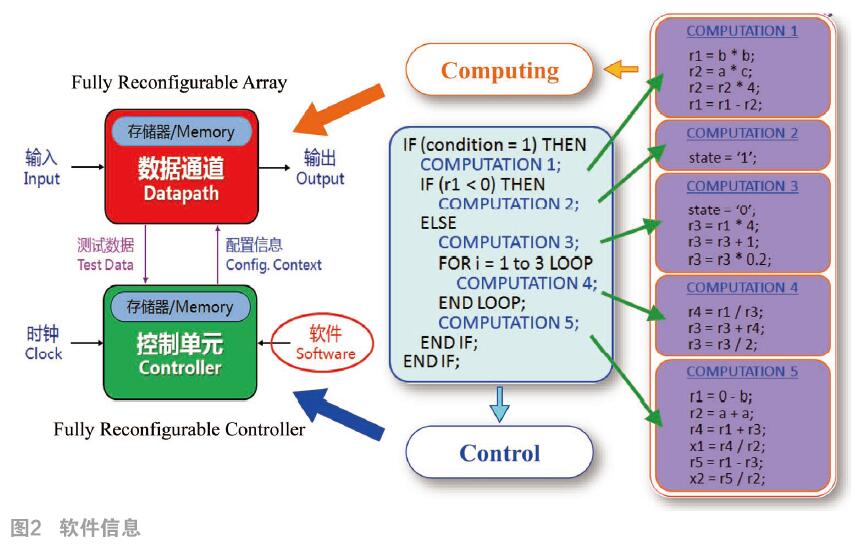

软件信息主要可以分为两类:计算信息和控制信息。如果我们将软件写成如图2所示形式,中间对应的是控制信息,用来控制程序执行流程,右边对应的是计算信息。如果将软件中的计算信息和控制信息分开,就可以找到相应的架构,包括控制单元和数据通道。

数据通道对应的是阵列,控制单元对应的是有限状态机,不论是阵列,还是有限状态机,都是完全可编程的。从而实现不同软件部分按要求搬进去执行,具体地,将分块软件按照他们的依赖关系送到数据通道中,通过数据通道配置其中阵列,并执行。

而在软件配置和执行过程中,如果整个系统是按照C语言编写的,通过编译器会产生一系列的控制流,最后在硬件芯片上运行。这种架构的独特之处在于采用控制流、数据流和配置流代替之前的指令集。

评论