数字时钟管理模块与嵌入式块RAM

3.数字时钟管理模块(DCM)

业内大多数FPGA 均提供数字时钟管理( 赛灵思公司的全部FPGA 均具有这种特性)。赛灵思公司推出最先进的FPGA 提供数字时钟管理和相位环路锁定。相位环路锁定能够提供精确的时钟综合,且能够降低抖动,并实现过滤功能。

本文引用地址:https://www.eepw.com.cn/article/201710/365603.htm4.嵌入式块RAM(BRAM)

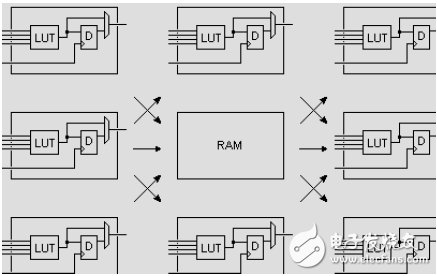

大多数FPGA 都具有内嵌的块RAM,这大大拓展了FPGA 的应用范围和灵活性。块RAM 可被配置为单端口RAM、双端口RAM、内容地址存储器(CAM) 以及FIFO 等常用存储结构。RAM、FIFO 是比较普及的概念,在此就不冗述。CAM 存储器在其内部的每个存储单元中都有一个比较逻辑,写入CAM 中的数据会和内部的每一个数据进行比较,并返回与端口数据相同的所有数据的地址,因而在路由的地址交换器中有广泛的应用。除了块RAM,还可以将FPGA 中的LUT 灵活地配置成RAM、ROM 和FIFO 等结构。在实际应用中,芯片内部块RAM 的数量也是选择芯片的一个重要因素。

图2-7 内嵌的块RAM

相关推荐

-

sandman555 | 2005-02-05

-

-

-

-

herbertwj | 2004-08-15

-

-

-

sandman555 | 2005-02-05

-

-

-

xiaohua | 2002-09-24

-

-

-

sandman555 | 2005-02-05

评论