PowerPC 440 处理器模块

面积利用率高、性能高的嵌入式系统 创新型 Virtex™-5 FXT 平台提供了一流的 FPGA,从而提供了2个带有32位 RISC 核的行业标准 PowerPC® 440 处理器(每个都在它自己的嵌入式外设模块内)。

简介

- 1,100 DMIPS @ 550MHz 处理器;利用带有2个处理器的单个 FPGA 实现了 2,200 DMIPS 的性能

- 新的5 x 2、128位纵横交换机实现了延迟最小化和点到点连接功能

- 同步存储器总线和处理器本地总线(PLB)接入实现了吞吐量最大化

- 集成式 DMA 通道、PLB 接口和专用存储器接口实现了逻辑资源利用最小化

- 辅助处理器单元(APU)控制器让硬件加速器整合变得很轻松

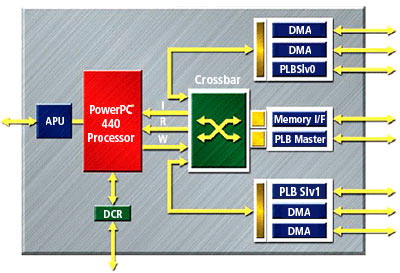

图1

PowerPC 440 处理器嵌入式模块。

本文引用地址:https://www.eepw.com.cn/article/201706/349531.htm深入探讨

整合了高速逻辑和软件灵活性

- 根据您的要求定制嵌入式系统设计

- 利用内置式 PowerPC 440 处理器模块设计片上系统功能和实时处理功能

- 利用 MicroBlaze™ 软处理器在全部 Virtex-5 FPGA 内有效地实现控制功能

实现最高吞吐量

- 获取到 TEMAC、PCIe 模块和 FPGA 逻辑的、无阻塞流水线点到点访问入口

- 利用每周期最高可以传输128位数据的专用存储器接口端口卸载 PLB

- 利用高度流水线化的发射和接收分散集中 DMA 通道实现数据传输速率的最大化

- 通过用户可选的端口优先化和工作频率来优化系统性能

提升系统性能

- 卸载 CPU 密集型操作,如视频处理、3D 数据处理和浮点数学运算

- 利用 APU 控制器在 FPGA 逻辑内创建定制协处理器

- 优化硬件/软件分区,从而实现 FPGA 利用率的最大化和硬件成本的最小化

- 利用 IEEE 754 兼容浮点单元选项实现双/单精度算术运算

简化嵌入式开发,推进创新

- 利用获奖的 Platform Studio 工具套件加快处理设计

- 利用设计向导、可定制 IP 和集成式 HW/SW 套件提高生产率

- 利用 Eclipse SDK 和 ChipScope™ Pro 集成式总线分析器简化系统级调试

- 行业领导厂商提供的大量的在实时 O/S、设计、调试和跟踪技术方面的ecosystem 支持

- 利用快速启动在嵌入式设计的最关键的项目阶段为您的队伍提供专家级建议和培训

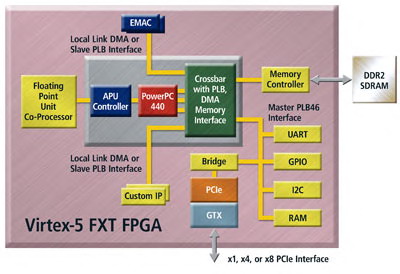

图2

PowerPC 440 处理器系统设计实例。

评论