Verilog串口通讯设计

随着多微机系统的应用和微机网络的发展,通信功能越来越显得重要。串行通信是在一根传输线上一位一位地传送信息.这根线既作数据线又作联络线。串行通信作为一种主要的通信方式,由于所用的传输线少,并且可以借助现存的电话网进行信息传送,因此特别适合于远距离传送。在串行传输中,通信双方都按通信协议进行,所谓通信协议是指通信双方的一种约定。约定对数据格式、同步方式、传送速度、传送步骤、纠错方式以及控制字符定义等问题做出统一规定,通信双方必须共同遵守。异步起止式的祯信息格式为:每祯信息由四部分组成:

a.1位起始位。

b.5~8位数据位。传送顺序是低位在前,高位在后.依次传送。

c.一位校验位,也可以没有。

d.最后是1位或是2位停止位。

FPGA(Field Pmgrammable Gate Array)现场可编程门阵列在数字电路的设计中已经被广泛使用。这种设计方式可以将以前需要多块集成芯片的电路设计到一块大模块可编程逻辑器件中,大大减少了电路板的尺寸,增强了系统的可靠性和设计的灵活性。本文详细介绍了已在实际项目中应用的基于FPGA的串口通讯设计。

本设计分为硬件电路设计和软件设计两部分,最后用仿真验证了程序设计的正确性。

2 系统的硬件设计

本方案的异步串行通信的硬件接口电路图如图1所示,主要由四部分组成:RS-485数据发送模块、FPGA串口模块、MAX3223和DB9。各部分功能简述如下:

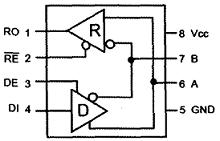

RS-485数据发送模块是将前续电路的数据发送到FPGA,供本电路处理,亦即本电路的输入。RS485是符合RS-485和RS-4225串口标准的低功耗半双工收发器件,有3.3V和5V两种,在本设计中选用了3.3V的器件SP3485。SP3485的内部结构示意图如图2所示

在本设计中。485的7脚和8脚与前端信号相连接,用于接收输入的数据。数据格式是这样的:一帧数据有25位,报头是16个高电平和1个低电平,接下来是 8位有效的数据。传输速率为700k波特率。2脚是使能端,与FPGA的I/O口相连,由FPGA提供逻辑控制信号。1脚和4脚也与FPGA相连,由 FPGA对输入数据进行处理。

FPGA串口模块是将由RS-485发送过来的数据进行处理,提取出8位有效数据,并按异步串口通讯的格式要求输出到MAX3223的12脚。FPGA选用Xilinx公司的Spartan II系列xc2s50。此部分为该设计的主体。如上所述,输入数据的传输速率为700k波特率。为了使FPGA能够正确地对输入数据进行采样,提高分辨率能力和抗干扰能力,采样时钟必须选用比波特率更高的时钟,理论上至少是波特率时钟的2倍。在本设计中选用4倍于波特率的时钟,利用这种4倍于波特率的接收时钟对串行数据流进行检测和定位采样,接收器能在一个位周期内采样4次。如果没有这种倍频关系,定位采样频率和传送波特率相同,则在一个位周期中,只能采样一次,分辨率会差。比如,为了检测起始位下降沿的出现,在起始位的前夕采样一次之后,下次采样要到起始位结束前夕才进行。而假若在这个周期期间,因某种原因恰恰使接收时钟往后偏移了一点点,就会错过起始位。造成整个后面位的检测和识别错误。针对本设计,FPGA的软件共分了三个模块:

1.时钟分频模块。模块的功能是用来产生所需要的数据采集时钟和数据传输时钟。系统主频是40M的。数据采集时钟是2.8M的,发送时钟是11.2k。

2. 提取数据模块。由RS485发送过来的数据共有25位,其中只有8位是有效数据。为了发送这8位有效数据。必须先将其提取出来。提取的办法是这样的:通过连续检测到的16个高电平和一个低电平。判断8位有效数据的到来。然后按照串行数据传输的格式,在加上起始位和停止位后,将其存储于输出缓冲寄存器中。在这里,我们的串行数据输出格式是这样规定的,一位起始位,八位数据位,一位停止位,无校验位。

3.串行数据输出模块。这一模块相对比较简单,波特率选为11.2k,模块的功能是在移位输出脉冲的作用下,将输出缓冲寄存器中的数据移位输出。

MAX3223是实现电平转换的芯片。由于RS-232c是用正负电压来表示逻辑状态。与TTL以高低电平表示逻辑状态的规定不同。因此,为了能够同计算机接口或终端的TTL器件连接,必须在RS-232与TTL电路之间进行电平和逻辑关系的变换。实现这种变换的方法可用分立元件,也可用集成电路芯片。 MAXIM公司的MAX3223是为满足RS-232c的标准而设计的具有功耗低、波特率高、价格低等优点,外接电容仅为0.1uF或1uF,为双组 RS232收发器。由MAX3223的12脚输入的数据,经过电平转换后由8脚输出,再经过DB9的TxD端输出,由PC机接收并做后续处理。

3 系统软件设计

FPGA模块是本设计的主体,使用Verilog硬件描述语言进行编写,本段代码共有两个子模块,分别实现提取八位数据和串行数据发送的功能。

下面是verilog源代码

module SIMO(din,clk,rst,dout_ser);

input din; //串行输入数据

input clk; //时钟信号

input vat; 复位信号

reg[7:0] indata_buf; //输入缓冲寄存器,存提取的有效位

reg[9:0] dout_buf; //输出缓冲寄存器,加了起停位

output reg dout_ser; //串行数据输出

reg nclk; //提取八位有效数据的采样时钟.是4倍于波特率的时钟

reg txclk; //发送数据时钟。发数据取11.2k的波特率

integer bitpos=7; //当前位

parameter s0=0,s1=1,s2=2,s3=3;

reg[2:0]state;

reg[4:0]counter; //用来计算报头报尾中1的个数

reg tag,tag1;

reg[2:0]cnt3;

reg txdone=1'b1;//一个字节数据传输完毕标志

*********提取有效数据位并按串行通讯格式装载数据********

always@ (posedge nclk or posedge rst) begin

if(rst)

begin

state=0;

counter=0;

tag1=0;

tag=0;

indata_buf=8'bz;

dout_buf=10'bz;

bitpos=7;

cnt3=0;

end

else case(state)

s0:begin

tag=0;//表示数据没有装好

if(din)

begin

counter=counter+1;

state=s0;

if(counter==15)//如果检测到16个1则转入s1状态检测接下来的是不是0

begin

state=s1;

counter=0;

end

end

else begin

counter=0;

state=s0;

end

end

s1:if(!din)//如果是0的话,转入s2状态,提取八位有效数据

state=s2;

else //否则转到s0状态重新检测

state=s0;

s2:if(cnt3==3)//是否采集四次数据

begin

cnt2=0;

indata_buf[bitpos]=din; //先进来的是高位数据

bitpos=bitpos-1;

if(bitpos==-1)

begin

bitpos=7;state=s3;end

end

else cnt3=cnt3+1;

s3:begin

tag1=tag;

tag=1'b1; //标志输入寄存器满。表明已把有用数据装入寄存器

if(tag~tag1)txdone) //检测到tag的上升沿以及txdone为高才把输入缓冲数据放到输出缓冲去

dout_buf={1'b1,indata_buf[7:0],1'b0};//停止位,高位,低位,起始位

state=s0;

end

endcase

end

//***********发送数据模块

reg[3:0] state_tx=0;

always@(posedge txclk or posedge rst)

begin

if(rst)

begin

dout_ser=1'bz;

state_tx=0;

txdone=1;

end

else

case(state_tx)

0:begin

dout_ser=dout_buf[0];state_tx=state_tx+1;txdone=1'b0;end

1:begin

dout_ser=dout_buf[1];state_tx=state_tx+1;end

2:begin

dout_ser=dout_buf[2];state_tx=state_tx+1;end

3:begin

dout_ser=dout_buf[3];state_tx=state_tx+1;end

4:begin

dout_ser=dout_buf[4];state_tx=state_tx+1;end

5:begin

dout_ser=dout_buf[5];state_tx=state_tx+1;end

6:begin

dout_ser=dout_buf[6];state_tx=state_tx+1;end

7:begin

dout_ser=dout_buf[7];state_tx=state_tx+1;end

8:begin

dout_ser=dout_buf[8];state_tx=state_tx+1;end

9:begin

dout_ser=dout_buf[9];state_tx=state_tx+1;end

endcase

end

endmodule

注:两个频率信号nclk、txclk由相应的分频程序产生。由于篇幅所限未在文中列出。

FPGA模块接收从RS-485发送过来的串行数据。25位为一个字符。数据的传输速率是700kbps,用四倍于波特率的速率进行采样,这样可以大大降低系统的噪声。数据的串行输出波特率选为11200bps。

由输入输出波形图可以看出:本段程序实现了对输入数据的有效数据位的提取,并按照一定的波特率进行串行输出。程序中,波特率可以根据需要通过分频程序进行改动。硬件电路搭建简单,程序代码书写容易。数据传输稳定可靠,可以满足串口通信的要求。

评论