基于FPGA的虚拟逻辑分析仪的设计

逻辑分析仪是一种通用数据域测试仪器。应用在由中大规模数字集成电路组成的数字系统中,主要查找总线相关性故障,能以多种方式跟踪与显示总线上的数据流,是测量领域不可缺少的工具。

随着电子技术和计算机技术的发展,逻辑分析仪与 PC机相结合,研发的虚拟逻辑分析仪是近年的一个新的发展方向,两者的结合扩展了逻辑分析仪的分析和计算能力,提高了性价比,且增强了仪器的通用性。现场可编程逻辑器件FPGA,是一种可由用户根据所设计的数字系统的要求,在现场由自己配置、定义的高密度专用数字集成电路。它具有设计方便、灵活、校验快和设计可重复改变的特点。

本文提出了一种基于FPGA的虚拟逻辑分析仪的设计方法。该系统对采集到的模拟或数字信号进行存储、预处理和逻辑分析。通过FPGA控制数据单次或连续采集、缓冲,通过PCI9030将缓冲区数据转移到硬盘管理卡,由硬盘管理卡将数据存入海量硬盘。

1 系统结构设计

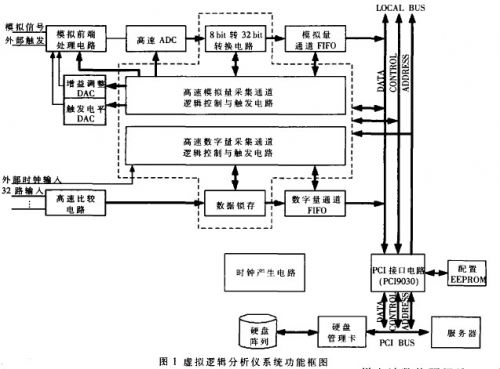

本文设计的虚拟逻辑分析仪主要由高速模拟量采集通道、高速数字量采集通道、PCI接口电路、时钟产生电路四部分组成。数据采集系统要解决的问题主要是数据的采集和传输问题。为了增强设计的灵活性和可扩展性,系统采用FPGA(Field Programmable Logic Array)来实现对A/D转换器、数据缓冲器、时钟、数据传输的逻辑控制。系统功能框图如图1所示。

2 FPGA在系统中的应用

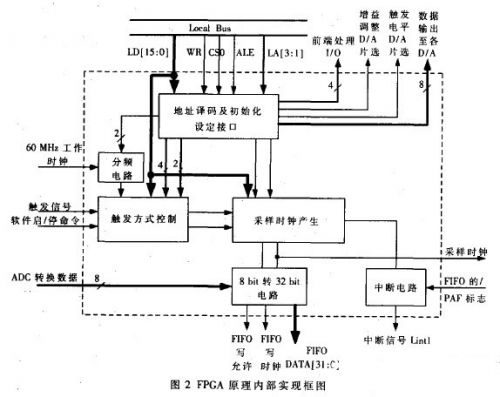

FPGA领域的快速发展使FPGA片上资源大量丰富,尤其是其高速性能和片上RAM使其特别适用于高速数据采集系统的设计。设计选用Altera公司的FLEX10K30E,该器件含有8个EAB(嵌入式阵列),每个EAB能够提供4 Kbit存储位,每个EAB都有双口RAM实现能力;提供30 000逻辑门;支持PCI总线,可提供 66 MHz的PCI性能;门级延时仅为6.5 ns。本系统中FPGA设计主要包含地址译码及初始化接口电路、分频电路、触发方式控制电路、采样时钟产生电路、8 bit转32 bit电路、中断电路等。FPGA功能框图如图2所示。

3 系统功能分析与系统描述

依据前面讨论的系统级设计方法,首先对高速模拟量采集通道逻辑控制与触发电路所应具备的功能进行分析。归纳出本部分电路应完成的功能主要有以下几点:(1)软件初始化设定的接口;(2)触发方式控制;(3)采样时钟产生;(4)启动/停止采样及数据的缓存与读取。

3.1 软件初始化设定

采集通道的初始化设定主要包括耦合方式选择、前端电路使能、触发源(内/外触发)选择、触发方式设定、采样方式及采样频率设定。这些设定均采用模拟量采集通道工作方式寄存器(16 bit)的各标志位来控制。工作方式寄存器作为Local Bus的I/O端口来操作。另外,还有触发延迟计数值预置端口、触发超前计数值预置端口、采样点计数值预置端口、增益调整D/A转换操作端口以及触发电平D/A转换操作端口等I/O端口。这些I/O端口组成一个连续的I/O地址范围,由Local Bus总线译码来寻址并进行相应I/O操作。

3.2 触发方式控制

本设计提供了三种常用的触发方式:立即电平触发、延迟电平触发、超前电平触发。根据外部触发信号选择所需的触发方式。

3.3 采样时钟

由于受高速ADC最低采样频率的限制(最低为5 MHz,低于此值会造成ADC的量化误差急剧增大,甚至ADC不能正常工作),因此,本文设计的异步采样提供了四种采样频率:由60 MHz有源晶振提供基准时钟送到FPGA的可编程分频器,经过可编程分频电路之后产生60 MHz、30 MHz、15 MHz、7.5 MHz四种时钟输出到触发方式控制器中。把时钟信号和触发方式送到采样时钟产生电路中产生系统需要的各个时钟信号。

3.4启动/停止采样及数据的缓存与读取

由计算机软件发出启动命令后开始采样,并同步将ADC输出的8 bit数据转换成32 bit存入FIFO中。若是单次采集(采样点规定小于16 K),则在采集完成后产生中断,由计算机一次性全部读回数据;若是连续采集,则当FIFO的可编程近满/PAF标志位有效时,产生中断信号,此时计算机响应中断后,仅依次读取2 K×32 bit的数据,由于采集数据从FIFO中读出比写入的时钟频率高很多,而采样还在继续,因此当/PAF再次有效时,计算机又读取同样的数据量,这样连续循环地进行,直到计算机软件发出停止命令才完成数据采集过程。

4 时序仿真分析

时序仿真是接近真实器件运行环境的仿真,仿真过程中已考虑了器件硬件特性,且时序仿真的网表文件中已包含了较为精确的延迟信息,因此仿真精度很高。

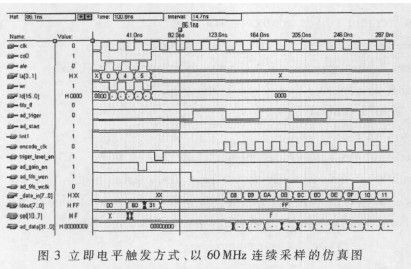

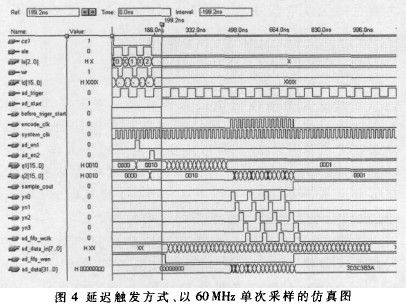

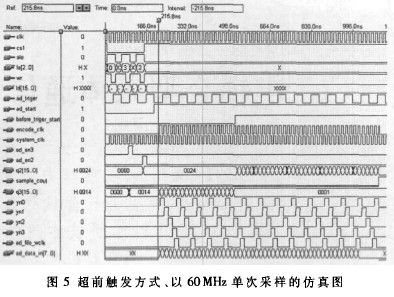

时序仿真环境按照数据采集的过程来建立,完成各种初始化设定后,主要注意触发控制、采样时钟的输出以及数据采集的启/停控制是否满足要求,如果没有达到设计要求,则必须对前面的设计描述加以修改,直到符合要求,才可以将产生的下载文件通过编程器或下载电缆载入目标器件FPGA中。仿真结果如图3~图5所示。

从时序逻辑图可知,触发控制、采样时钟的输出以及数据采集的启/停控制满足系统要求。可以将产生的下载文件通过编程器或下载电缆载入目标器件FPGA中。

经测试表明,本文设计的虚拟逻辑分析仪系统稳定,工作状态良好,具备了较强的逻辑分析能力,能满足信号分析的要求。由于该方案基于Altera公司的EPF10K30E系列FPGA来实现,使部分硬件功能软件化,使硬件电路大为简化,提高了逻辑分析仪的可靠性,降低了成本,且功能易于扩展,具有一定的教学和科研价值。

评论