硬件描述语言Verilog HDL设计进阶之: 典型实例-状态机应用

4.6典型实例6:状态机应用

4.6.1实例的内容及目标

1.实例的主要内容

状态机设计是HDL设计里面的精华,几乎所有的设计里面都或多或少地使用了状态机的思想。状态机,顾名思义,就是一系列状态组成的一个循环机制,这样的结构使得编程人员能够更好地使用HDL语言,同时具有特定风格的状态机也能提高程序的可读性和调试性。

本实例通过设计一个状态机来控制红色飓风II代Xilinx开发板上面的8个LED灯循环闪烁。在本实例状态机的设计过程中,读者需要着重注意状态机设计的一些特性。

·FSM设计方法(米勒型和摩尔型)。

·状态机的编码(Binary、gray-code、one-hot等)。

·状态机的初始化状态和默认状态(完整状态机设计)。

·状态机的状态定义风格(使用parameter参数定义状态)。

·状态机的编写风格(状态任务与状态转换分离)

2.实例目的

通过本实例,读者应达到下面的目标。

·熟悉XilinxISE开发环境。

·熟悉红色飓风II代Xilinx开发板的使用。

·了解状态机设计输入方法。

·掌握状态机在系统设计中的应用。

4.6.2实例详解

本实例的具体步骤可参见2.6节,在此不再详述,仅给出主要的操作流程以及状态机的设计输入方法。

(1)启动ISE软件。

(2)创建新工程。

(3)编写状态机Verilog代码。

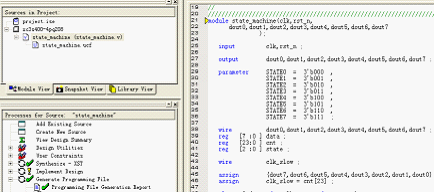

状态机的代码可以直接进行手动编写,如图4.2所示。

图4.2手动编写状态机代码

对于简单的状态机,使用手动输入的方式进行编写是最直接的。但是如果需要进行复杂的状态机设计,使用状态图设计输入方式则会更加方便。下面介绍使用状态图进行状态机设计的一般步骤。

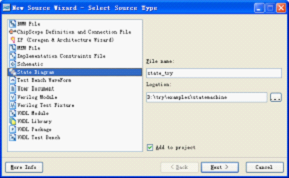

使用ISE创建工程后,为工程添加新的设计输入,选择“StateDiagram”选项,如图4.3所示。

图4.3状态图设计输入方式

此时ISE将打开如图4.4所示的StateCAD工具进行状态机设计。

图4.4StateCAD状态机设计工具

在这个专门的工具中,读者就可以很方便地进行状态机的设计。使用这个工具进行状态机设计的步骤主要分为3个,下面分别介绍。

(1)创建状态机。

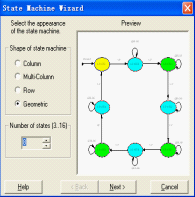

单击工具栏上的 图标,打开状态机输入向导,如图4.5所示。

图标,打开状态机输入向导,如图4.5所示。

在本实例中,我们在向导第1页设置一个8状态的状态机,如图4.5所示。在该页中,还可以设置状态机图形的形状。在对话框的右侧有图形的预览效果,用户可根据自己的喜好设置图形的形状。

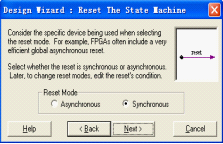

在状态机向导的第2页,我们为状态机使用同步复位模式,建立一个同步状态机,如图4.6所示。

图4.5状态机向导 图4.6同步状态机

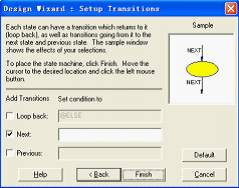

在状态机向导的第3页,可以设置状态机的转换模式,本实例中使用Next转换模式,如图4.7所示。

图4.7状态机转换模式

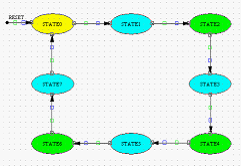

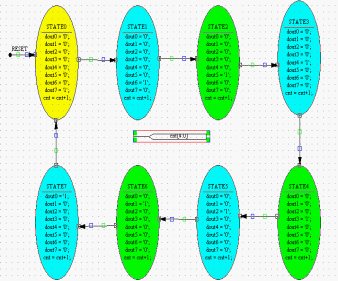

设置完毕后,单击“Finish”按钮即可完成状态机的创建。在StateCAD工具的工作区将出现如图4.8所示的状态机图形。

(2)添加状态任务。

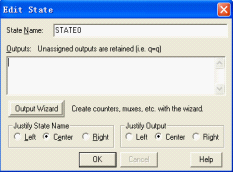

创建状态机后,就要为其中的每一个状态添加状态任务。首先,双击如图4.8所示的图形中的STATE0状态,为STATE0添加任务。此时,将出现如图4.9所示的状态任务编辑器。

图4.8创建的状态机

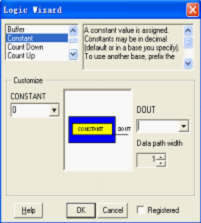

单击“OutputWizard”按钮,打开输出向导对话框,如图4.10所示。

图4.9状态任务编辑器 图4.10状态输出向导对话框

在输出向导对话框里面有很多可以选择的逻辑,根据不同的需要选择逻辑资源,并输入参数。单击“OK”按钮即可完成对STATE0的状态任务编辑。

按照相同的方法分别为每个状态加载任务,得到如图4.11所示的状态机。

(3)添加状态转换条件。

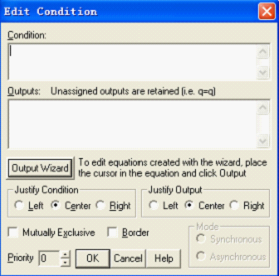

设置完状态任务后,还需要为状态之间的转换调价条件。可以双击两个状态之间的连线设定状态转移条件,此时将出现条件编辑器,如图4.12所示。

在该对话框中,可以在“Condition”下面填写转移条件(例如:cnt=10),也可以单击“OutputWizard”按钮打开输出向导进行设置。设置结束后,单击“OK”按钮,完成两个状态之间的转换条件设置。

图4.11添加任务的状态机图形

图4.12状态转换条件编辑器

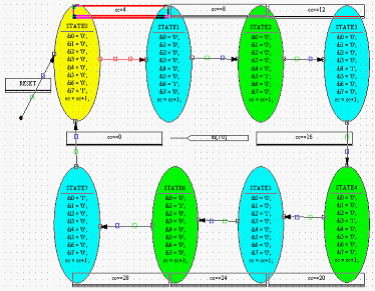

按照同样的方法为需要添加转换条件的状态连线加载状态转移条件。完成后,得到如图4.13所示的状态机。

至此,一个基本的状态机已经建立完毕。这样的一个状态机已经可以在我们的系统中使用。不过在使用之前,我们还需要为StateCAD工具做一些设置,才能使图形形式的状态机转化为HDL语言的形式。

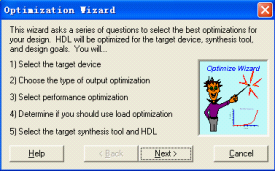

1.优化设置

首先对状态机进行优化设置,选择StateCAD工具条上的 按钮,打开优化设置向导,如图4.14所示。

按钮,打开优化设置向导,如图4.14所示。

图4.13添加状态转换条件的状态机

图4.14优化设置向导

在如图4.14所示的向导中,提示将进行5个步骤的设置,下面分别介绍。

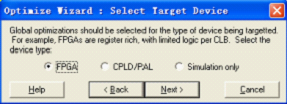

①选择目标器件。本实例中选择FPGA,如图4.15所示。

图4.15选择目标器件

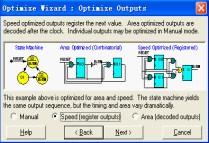

②选择状态机的优化方向,用户可以选择速度优先、占用面积优先以及手动设置。在本实例中我们选择速度优先,如图4.16所示。

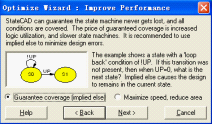

③对状态机的性能改善方式进行选择,如图4.17所示,本实例选择保证覆盖面积模式。

图4.16状态机优化方向

图4.17状态机性能改善模式

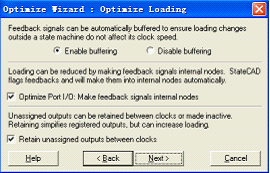

④加载优化参数设置,如图4.18所示。

图4.18加载优化参数设置

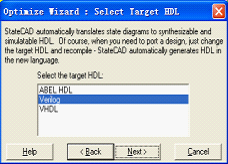

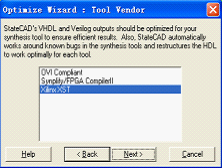

⑤为状态机选择输出的HDL语言形式以及综合的EDA工具。在本实例中,选择Verilog语言及XilinxXST综合工具,如图4.19所示。

图4.19选择目标HDL语言和EDA工具

经过这5个步骤的设置,就完成了状态机的优化设置,可以开始生成Verilog语言形式的状态机了。

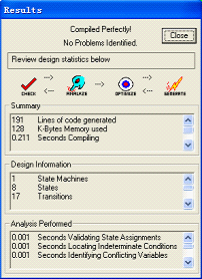

选择StateCAD工具栏上的 按钮,开始生成Verilog状态机。如果设计没有错误,将出现如图4.20所示的结果对话框。

按钮,开始生成Verilog状态机。如果设计没有错误,将出现如图4.20所示的结果对话框。

图4.20状态机生成结果

单击“Close”按钮后,就可以看见生成的与状态机名称相同、后缀为.v的源文件了。

2.添加设计输入

将使用StateCAD生成的状态机源文件加入工程中,即可查看并编辑相关的状态机的代码了。

3.设置器件及管脚约束

按照开发板的说明进行相关的设置。

4.下载验证

本实例的状态机在开发板上下载后,将能看到开发板上的8个LED循环变亮,即实现跑马灯的功能。

4.6.3参考设计

本实例相关参考设计文件在本书实例代码的“典型实例6”文件夹。

评论