SoC时代推动验证革新 硬件仿真走向新高度

SoC时代的经济正在推动验证的革新。革新的关键特征是 SoC(片上系统)中的 “S”(系统)。虽然芯片已经变得更加复杂,但是用“复杂”来描述这场验证革新的关键驱动因素并不充分和准确。如今,芯片验证已经成为系统级验证和确认,由此会产生各种影响。

本文引用地址:https://www.eepw.com.cn/article/201610/308105.htm更多、更大型的系统设计以及嵌入式软件的重要性不断提高,这意味着更多的公司需要进行硬件仿真,更多的设计团队需要介入到从模块级一直延续到系统级的工作。他们需要一个整体的软件仿真到硬件仿真流程,以便能够将他们在模块级已经完成的艰苦工作带入子系统和系统级并进行重复利用。这样可以节省大量时间,并提高验证的质量和工作效率。例如,不必在每次将更多模块和子系统结合在一起时都要编写新的测试平台。

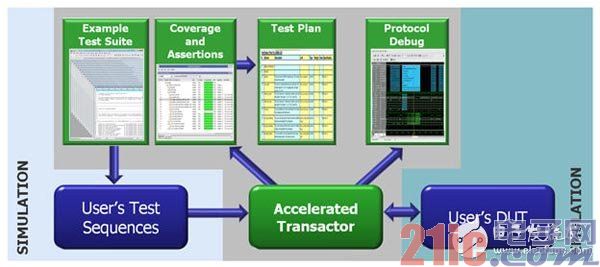

要实现这一整体流程,在主机工作站和硬件加速器之间建立一个超高速的串行连接(称为co-model协同建模通道)来传输数据包是非常关键的。在协同建模中,运行在工作站上的为高级软件仿真验证所创建的可复用测试平台,通过transactor事务处理器连接到硬件仿真器,事务处理器和DUT一起都放在硬件加速器上。这些加速的事务处理器会将高级事务转换为信号级激励来驱动DUT,从而使硬件加速器能够以软件模拟器10,000倍的速度来实现验证。提高这些速度所需的协同建模通道性能取决于快速的物理链接和高度优化的软件层;迄今为止,这仅适用于Veloce 平台。

以此令人炫目的速度交换事务的能力使协同建模接口成为灵活、多层面流程的理想通道,这样可在软件仿真和硬件加速中使用相同的采用统一验证方法学(UVM)的 测试平台、验证IP、覆盖率统计、断言、采用通用功耗格式 (UPF)的功耗感知技术以及调试工具。甚至可以在同一工作站上运行所有这些技术,并且硬件加速器可以将覆盖率和断言数据回馈到同一个通用覆盖数据库 (UCDB) 中。

图1. 在模拟器和仿真器之间通过协同效应建立整体软件仿真到硬件仿真流程。

这样,可以从根本上转换硬件加速器的使用模型。其中一个重要好处是硬件加速器仍然可以加速软件仿真,但它所做的远不止如此。它允许用户使用软件和所有外围设备(无论是在线仿真 (ICE) 硬件外围设备,还是虚拟软件外围设备)执行完整的芯片验证。此外,还允许将在设计仿真中所做的大量工作(包括测试平台和验证IP)转移到硬件加速器中。

要充分利用硬件仿真投资并将其作为真正的企业验证资源,硬件仿真必须经历一场从项目绑定工程实验室仪器到数据中心托管全球资源的变革。这场变革首先要消除ICE设置中混乱不堪的电缆、速度适配器以及物理设备,并将它们替换为虚拟设备。例如,可立即对Veloce VirtuaLAB外围设备进行重新配置,以便支持多个项目和瞬息万变的优先级,因为常见外围设备(如USB、以太网、PCIe和多媒体)的这些虚拟模型托管在标准数据中心计算机,而不是专有的硬件目标上。虚拟外围设备将硬件加速器带出实验室并置入数据中心,因此可供多个设计团队在多个位置使用。这样,不仅公司可以使用其仿真器来做更多的事情,整个公司的所有人都可一直使用它。

要让负责不同项目的多个工程师能够在此级别访问公司的仿真环境,企业服务器软件需要有效管理全球仿真资源,将这些资源整合到商业队列管理器中,成为一个高容量的实体。企业服务器要确定运行每项工作的最有效位置,并通过暂停较低优先级的工作来立即对高优先级工作提供支持。

采用此整体软件仿真和硬件仿真流程,设计人员可通过增加最少的工作量来获取全面的功能验证,因为所有这些技术已跨软件仿真和硬件仿真平台进行集成。用户可在很大程度上相信他们能够以最少的工作量使其SoC进入投片阶段。同样,他们可以用更短的时间实现覆盖,并有更好的机会如期实现其验证目标。

评论