基于FPGA的多路视频收发系统的设计与实现

摘要:为了实现对多路视频和数据信号的同步传输,提出了一种基于FPGA的视频数据综合传输系统设计方案,并完成系统的软硬件设计。该系统的硬件部分主要由FPGA、CPLD芯片及光模块等设备组成,软件部分采用VHDL语言进行逻辑编程,能够完成整个收发系统的全部功能。实际工程应用表明,该系统具有成本合理、操作简便、性能稳定的特点,达到了设计要求。

本文引用地址:https://www.eepw.com.cn/article/201610/307180.htm随着人们安全意识的不断提高,对现代化视频监控技术也有了进一步要求,先进的视频、音频、数据的综合传输设备得到广泛的应用,因此,对综合业务传输性能的要求也越来越高。如何在控制成本的基础上,开发性能稳定、信号完整的综合传输系统,是广大传输设备开发工程师需要思考的问题。目前,在成本有限的情况下,市面上所见的综合业务传输设备大多有性能不太稳定、传输类型单一、容易乱码、断网等缺陷。比如,仅可收发视频信号,没有语音信号,或是数据信息有缺失、画面抖动、时断时续的现象。因此,做到视频、数据、语音等多种信号的同步、稳定叠加,对于整个综合业务传输设备在成本控制的情况下,产品还有很大的提升空间。

在压缩工程应用成本的基础上,对视频、数据、语音等信号的安全、有效传输将是本文的研究重点。为了实现对综合业务的准确传输,在做了详尽的需求分析基础上,提出并设计了一种基于FPGA的多路视频收发系统(以下简称“收发系统”)的硬件及软件设计方案。经多次测试及工程实际应用表明,该系统能很好地完成综合业务的有效传输。

1 总体设计

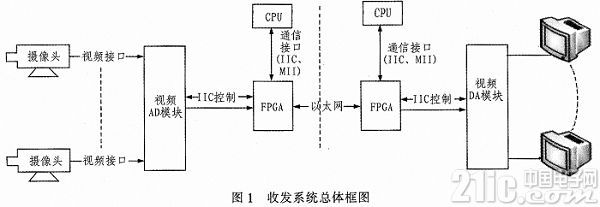

整个系统由两端设备组成,两端构成基本相同。习惯上,通常把视频信号输入的一端称发送端,另一端则为接收端。发送端由摄像头采集视频信号,经AD转换模块,将模拟信号转换为数字信号,经处理的数字视频信号及其他数据信号在FPGA中进行编码操作。其中,部分控制信号由外处理器给出指令。FPGA编码处理后的信号,由光模块经千兆以太网传输至接收端。在接收端,FPGA负责将千兆以太网传输过来的编码数据进行解码,部分指令仍由外处理器给出。处理好的数字视频及其他数据经DA转换模块,将数字信号转化为可识别的模拟信号,最终在显示器上显示出来。图1给出“收发系统”总体框图。

本着节约成本、降低功耗、有效与其他设备通用的原则,整个系统硬件采用基板和背板的形式,这也是目前电子、通信行业最为流行的一种设备安装模式。设备核心为基板,负责完成高速数据复分接和光通道的建立,提供各种功能扩展接口,同时也提供最多4个视频通道,剩余6路视频信号则在视频扩展板内完成通信。在背板的基础上,插接各种功能的基板、扩展板。辅助通道扩展板通过背板与基板实现电源和信号连接,辅助通道扩展盘同时完成信号的中继。将信号的传输分为各个单板来实现。此种结构,简洁、大方、操作便利、便于纠错。

2 系统硬件设计

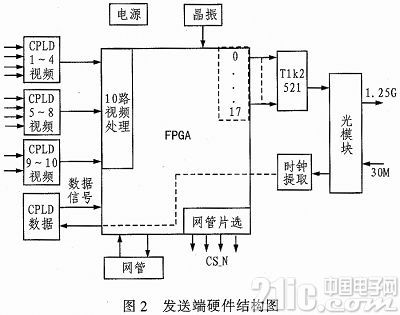

由于收发两端的结构基本一致,这里仅发送端为例,概述系统核心板的硬件设计。发送端主要由基板、视频扩展板、辅助通道扩展板1、辅助通道扩展板2等部分组成。其中以基板为核心,发送端硬件由FPGA主芯片、CPLD芯片、光模块及其他一些外围电路组成。FPGA主芯片负责处理十路视频信号复分接及片选信号的复用,网管送信号入FPGA后,由3—8译码器翻译出5种情况,分别送至4块CPLD芯片和本身的FPGA,通过填报不同的网管信息,上报各个芯片的运转情况。最终,由千兆收发器Tlk2521串行编码,经1.25 G光模块发送至接收端。

时钟方面。晶振选用67.5 M,以67.5 M作为基本速率。Tlk2521并行处理的速率为67.5 M.正向光传输信号的速率为1.25 G。发射端的基本时钟用当地时钟,接收端用还回时钟。收端送来的反向数据,由时钟提取电路提取出时钟和数据之后,送入FPGA进行同步处理。其结构图如图2所示。同步处理过程,将在FPGA的逻辑设计中进行详细描述。

视频信号采用8 bit量化方式,以13.5 M进行采样。通过四路、四路、二路复接的形式送入FPGA中,再通过FPGA整合成10路16 bit的形式,由Tlk2521处理后送到光模块中。同时,数据、音频、网管等辅助业务的数据则由单独的一个CPLD进行整合,通过一条线送入FPGA中,与视频信号一起形成17 bit的数据进行传输,同步字由20位构成,利用其中1 bit进行传输。TLK2521有18 bit并行数据线,其中每根数据线占67.5M的带宽,具体使用分配如下:0~7、8~15 bit传视频数据,第16 bit传辅助业务数据,第17 bit传输同步字。高速信号采用16 bit并行扰码,并行扰码跟帧同步保持同步,使用20个扰码字。

3 系统软件设计

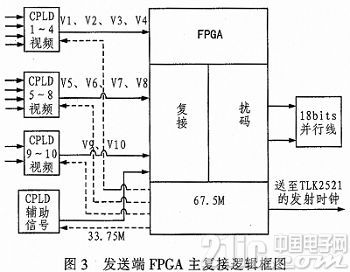

该收发系统FPGA芯片模块编写所使用的软件为ISE,采用VHDL语言编程。VHDL是当前FPGA芯片编程常用的描述语言,其功能强大、设计灵活、支持广泛、易于修改,具有强大的系统硬件描述能力、很强的移植能力、易于共享和复用。1~4路视频信号经CPLD汇总接入基板,5~8路视频信号经CPLD汇总,与9~10路视频信号以及辅助信号一起经过复接,接入FPGA中,最后将所有信号经扰码以18 bits并行数据线给出FPGA芯片。FPGA提供67.5 M采样始终给千兆位串行收发器TLK2521。图3给出发送端FPGA芯片复分接框图。

在基板视频复接中,通过FPGA送来的复接指示信号进行视频复接,由CPLD本身产生的一个计数器对时钟进行计数,5个时钟周期为一个计数周期,为4路视频开辟5个位置,把4路视频依次复接,第5位置空出不填充数据,有效地错开位置,从而实现非缓存的数据传输。在扩展板视频复接中,复接的方式和基板视频复接原理一样,不同之处在于,复接的位置不一样,扩展板的CPLD1在复接视频时空出的第1个位置;CPLD2在复接时,由于只有2路视频需要复接,所以第2、3、4位置空出。

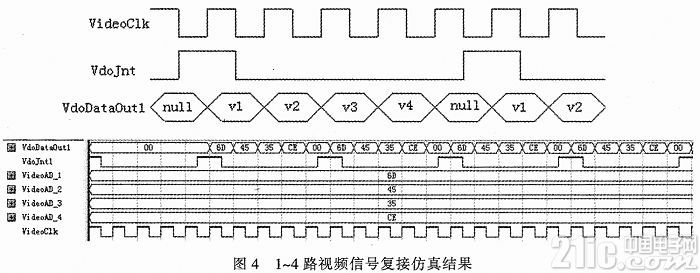

图4以1~4路视频信号复接为例,给出时钟关系仿真图。其中Vclk为67.5 M的时钟信号;VdoJnt为视频通道指示信号,一个时钟周期宽度的脉冲信号,在67.5 M时钟频率下,每5个周期送出一个脉冲,VideoClk和VdoJnt都由FPGA送往CPLD;VdoDataOut1为4路视频数据复接后的信号,此处按8 bits量化来定义;当复接指示VdoJnt为高电平,且在时钟VideoClk的上升沿时,对视频进行采样复接,最后复接成VdoDataOut1信号送出。

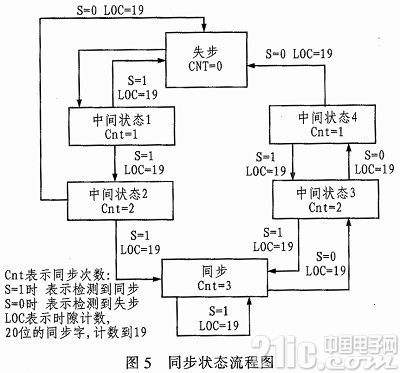

众所周知,在FPGA逻辑设计中,最重要的是时钟同步问题的解决。图5给出FPGA同步状态流程图,其中,Cnt表示同步次数,S=1表示检测到同步,S=0表示同步丢失,LOC对时隙计数,一共有20位同步,从0计数到19依照流程图编写同步判定程序,可完好地实现信号同步。

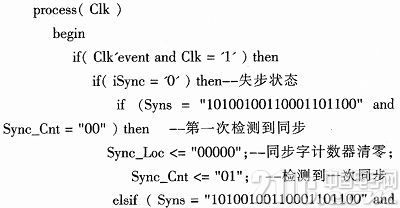

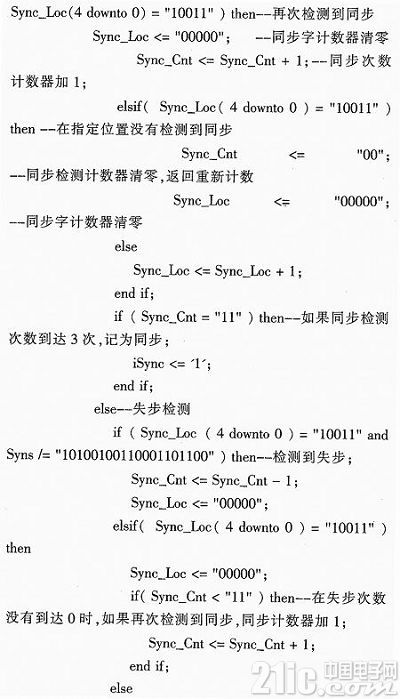

下面给出同步检测模块的部分程序,用来做同步和失步的检测。

4 研发过程中出现的问题、解决办法及效果

1)无视频。FPGA的程序下载之后,视频丢失,检测AD和DA的输入时钟,发现DA时钟输入异常。原因是配置管脚错误,按着电路原理图上说明的把DA管脚全部配置反了,后来修改过来之后视频正常。

2)视频位置错乱。收端按照发端复接视频的顺序分接视频,发现视频顺序错位,1234分别成了2341,原因:传输延迟造成了视频位置错位,修改接收端CPLD程序,调整分接位置之后,视频正常。

3)视频出现花屏。分接之后的视频有“花屏”现象出现,原因:时钟沿采样不准确。通过调整时钟沿解决,把送入CPLD的时钟取反,“花屏”现象消失。

4)视频扩展板视频指示灯异常。视频扩展板指示灯异常,处于常亮状态。原因:视频指示灯短路。用万用表查找时,发现在钽电容的下方,多出了的焊锡把钽电容下方的视频指示灯的过孔堵住了,使得视频线路短路,卸掉钽电容后小心焊接,问题解决。

5)插拔光纤时同步丢失,并死机。在测试网管的时候,进行插拔纤测试时,一旦拔掉光纤,再接上会造成同步丢失并死机,需要重新烧写程序方能解决。调整时序约束,把晶振时钟的时序约束调整到100 M,问题解决。

6)开关电数据误码。在进行开关电测试时,发现数据误码,且收光指示灯闪烁异常。参阅FPGA时序约束文章发现,时序约束不宜过高,把原来LockID的时序设置为100 M改为80 M之后,问题解决。

5 结论

该“收发系统”是在充分的理论分析与市场需求基础上做出的系统设计,经过详尽的测试转化为实际产品,该产品有效地降低了成本、提高了系统集成度,在一根光纤上实现了多种业务的综合传输,已应用于某安防系统,实际工程应用表明该系统具有收发信号准确、稳定性高、人机界面友好、易于操作、成本合理等特点,达到了设计要求。解决了实际工程应用中,低成本产品性能相对较差的缺陷,工程应用反应良好。

评论