基于X86平台的ARM指令集模拟器的设计

摘要:随着嵌入式系统软件的发展,以及嵌入式应用在各个行业的普及,嵌入式系统开发已经被越来越多的人所关注。目前,嵌入式软件更新频率快,因此要求开发者在短期内能开发出具有针对型的应用程序,然而嵌入式系统运行环境往往是用户制定,并且运行在特定的硬件环境中。常规的软件开发方法往往导致嵌入式系统开发效率低下,同时大幅提高了开发成本。因此,实现对嵌入式系统硬件环境的仿真能有效提高嵌入式系统开发效率。本文针对此问题,结合现有ARM体系架构和指令集模拟器实现原理,提出了一套基于X86平台的ARM指令集模拟器的设计方案。

关键词:嵌入式系统开发;ARM体系架构;指令集模拟技术;ARM指令集模拟器

如今,仿真技术和虚拟技术被广泛应用各个领域,特别在嵌入式系统的开发过程中,由于在不同应用领域中,嵌入式开发要求的硬件体系差别很大,用软件进行系统仿真或虚拟硬件非常必要。软件仿真的重点是微控制器的仿真,而对微控制器的仿真重点又在指令仿真上,因此本文给出一种基于解释型仿真策略的指令仿真器的实现。指令集仿真器(Instruction Set Simulator,ISS)是用来在宿主机仿真另一种目标机上程序运行过程的软件工具。它通过仿真每条指令在目标处理器上的执行效果来仿真目标机程序,是目标处理器的软件仿真器。在嵌入式软硬件的并行开发中,指令仿真器是必不可少的工具之一,在目标机可用之前,通过它就可以完成软件的仿真调试,真正做到了软硬件的并行开发。

1 ARM体系架构及指令集模拟技术

1.1 ARM体系架构

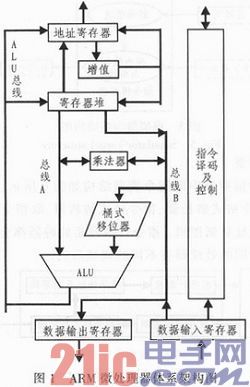

到目前为止,ARM微处理器以其体积小、低功耗、低成本、高性能、指令执行速度快、寻址方式灵活简单、执行效率高、指令长度固定等优点几乎已经深入到各个领域。ARM处理器实现加载/存储(load/store)体系结构,是典型的RISC处理器。只有加载和存储指令可以访问存储器。数据处理指令支队寄存器的内容进行操作,传统的CISC(Complex Instruction Set Computer,复杂指令集计算机)技术的指令集随着计算机的发展引入了各种各样的复杂指令,已经不堪重负。图1描述了ARM微处理器的体系架构。

1.2 指令集模拟技术

1.2.1 指令集模拟解释型模拟技术

解释型模拟器的模拟流程是参照硬件环境中的指令执行,并不进行任何执行信息的服用,故执行起来性能不高,爱目前主流配置的主机上的运行性能能一般从几十到几百个KIPS(Kilo-Instructions Per-Second)。由于解释型模拟器实现较为简单,同时能够提供足够的模拟精度以及灵活性,但解释型模拟器的模拟性能低下,故在对于模拟性能没有特别高的要求下,采用这种模拟技术是非常优越的。目前绝大部分商用的模拟器是解释型模拟器。这类模拟器的典型代表是SimpleScalar。

1.2.2 指令集模拟器动态翻译模拟技术

动态翻译模拟是在解释型模拟技术基础上的一种优化,由于使用了缓存技术尽可能大的复用已解析的信息,提高了模拟的效率。模拟器的工作流程是:模拟一条指令,先核对这条指令是否存在于缓冲页,如果是,则调用存储中已有的解码结果,实现模拟;如果没有,则翻译该指令并将结果缓存页中备用,同时按照解释型模拟的模式,继续进行。由于启动模拟编译器的系统开销较大,为了提高性能,每次启动模拟编译器完成若干条指令的翻译,为了处理方便,每次编译的指令数是固定的,称为一个“翻译页”。在动态翻译模拟技术中,翻译和模拟的过程耦合度较低,可以分配给不同的线程完成,或结合多核技术,将代码的执行工作分配给几个CPU同时来执行,来提高模拟速度。目前采用动态翻译技术的应用的较好的模拟器有Intel IA-32 Execution Layer等。

2 ARM指令集模拟器的设计

2.1 ARM指令集模拟器系统总体框架设计

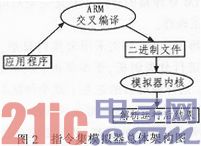

本模拟器的主要功能是模拟ARM处理器对指令集的处理能力,当把内容为ARM指令的二进制BIN文件输入时,可以模拟在真实ARM处理器上的运行效果。由图2指令集模拟器的总体架构图可以看出一个应用程序在运行的时候和指令集模拟器之间的关系。一个应用程序在经过ARM交叉编译器编译生成基于ARM指令集的二进制可执行文件,可执行文件进入ARM指令集模拟器内核被解释执行,最后得到运行后的结果。

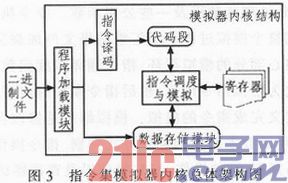

其中模拟器内核是整个模拟器的核心部分,也是本文将要重点设计和实现的部分。它主要包含一下功能:对可执行文件的加载,执行取指令、指令译码、指令模拟执行的三级流水和解析结果的展示。在模拟器内核设计部分,模拟指令执行的过程是内核的核心部分,在本模拟器设计中,借鉴CPU模型中的指令流水设计内核翻译程序的取指、译码和指令执行3个过程。图3描述了指令集模拟器内核的总体架构。如图所示,整个内核包含程序加载模块、指令译码模块、取指模块、指令调度与模拟模块、寄存器模拟模块和数据存储模块。在此模拟器中,存储模块不做实现,调用gdb中的相应模块。

评论